表2.5.2中定义了 4 种驱动强度和 3 种电荷存储强度:驱动强度与 gate output 和 continuous assignment有关;电荷存储强度用于 trireg 类型 net. (see

clause 28

gate-level and switch-level modeling)

-

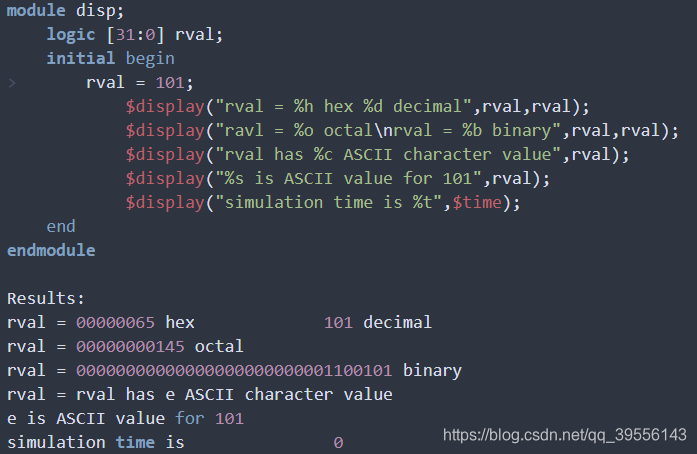

%s or %S 格式说明符用于将ASCII代码以字符样式打印。

-

对于出现在字符串中的每个%s,相应的参数应遵循参数列表中的字符串定义。

-

相关参数被映射为一个8位十六进制ASCII码序列,每8位代表一个字符。

-

如果参数是变量,则其值是右对齐的,以便该值的最右边的位是字符串中最后一个字符的LSB。

-

字符串末尾不需要终止字符或值,并且永远不会打印前导零(leading zeros)。

-

打印字符串时,一般使用%s即可满足要求,可以打印出全部字符。

>>

IEEE Standard for SystemVerilog - Unified Hardware Design, Specification and Verification Language, 1800

TM

-2017

>>

clause 21 Input/output system tasks and system functions

转载请注明出处!

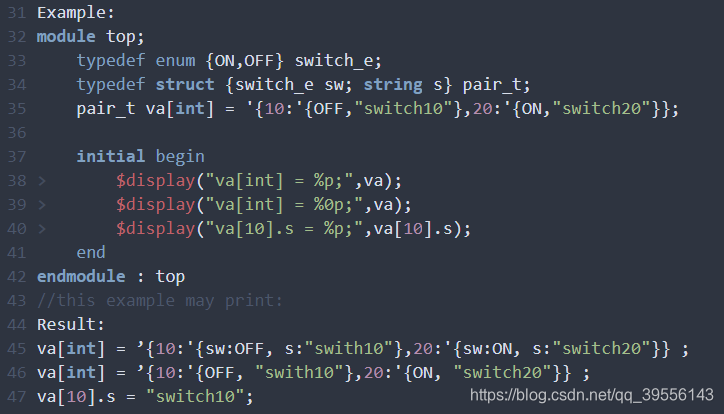

system_verilog display format1. 简介$display 和 $write的区别:$display系的系统函数:会在输出的末尾自动添加换行符(newline character);$write系的系统函数:光标会停留在输出的末尾,不会自动换行。$display 和 $write相同之处:按照参数列表的顺序输出参数;参数可以是引号内的字符串(quo...

$fmonitor(file_id, "%format_char", parameter);

$fmonitor(file_id, "%m: %t in1=%d o1=%h", $time, in1, o1);

Verilog

本质上也是一门高级语言,因而也提供了丰富

打印

信息、输出信息的系统函数。

Verilog

提供的

打印

系统函数分为三类:

显示/写系统函数(Display and Write tasks)

脉冲选择监视系统函数(strobed monitoring tasks)

连续监视系统函数(continuous monitoring tasks)

显示/写系统函数

这类函数包括$di

AD9361是ADI公司开发的一款高性能、低功耗软件无线电(SDR)解决方案。ad9361_init_

verilog

是AD9361芯片的初始化程序,开发者可以通过该程序来初始化AD9361芯片,以便实现不同的无线电应用。

ad9361_init_

verilog

程序实现了AD9361芯片的初始化,并提供了一些重要的配置选项。在使用AD9361芯片之前,必须对其进行初始化。在初始化过程

中

,需要设置

中

心频率、带宽、增益、采样率等参数,以便AD9361芯片能够根据应用的需要进行正确的工作。

为了使ad9361_init_

verilog

程序正常运行,需要先安装AD9361芯片和相应的开发环境。可以使用Vivado等工具来编译和生成bitstream文件,然后将bitstream文件烧写到FPGA芯片上。

调试ad9361_init_

verilog

程序时,需要注意一些常见的问题,如时钟频率、寄存器配置、数据

格式

等。此外,也可以通过读取AD9361芯片的状态和运行日志来进行问题排查和优化。

总之,ad9361_init_

verilog

程序是AD9361芯片初始化的关键之一,对于实现高性能、低功耗的SDR应用具有重要意义。