PowerPC技术与市场杂谈

PowerPC技术与市场杂谈

参考文献链接

https:// mp.weixin.qq.com/s/8tt6 tYlupYFs5AObyD8V6g

https:// mp.weixin.qq.com/s/Pzqo kak-fyLBsFFbE4PgSQ

https:// mp.weixin.qq.com/s/1xND e1PBdBQncAxWj2B5Dw

https:// mp.weixin.qq.com/s/2rxJ nsU0_HWlFc3PQE9wGA

PowerPC 架构和产品

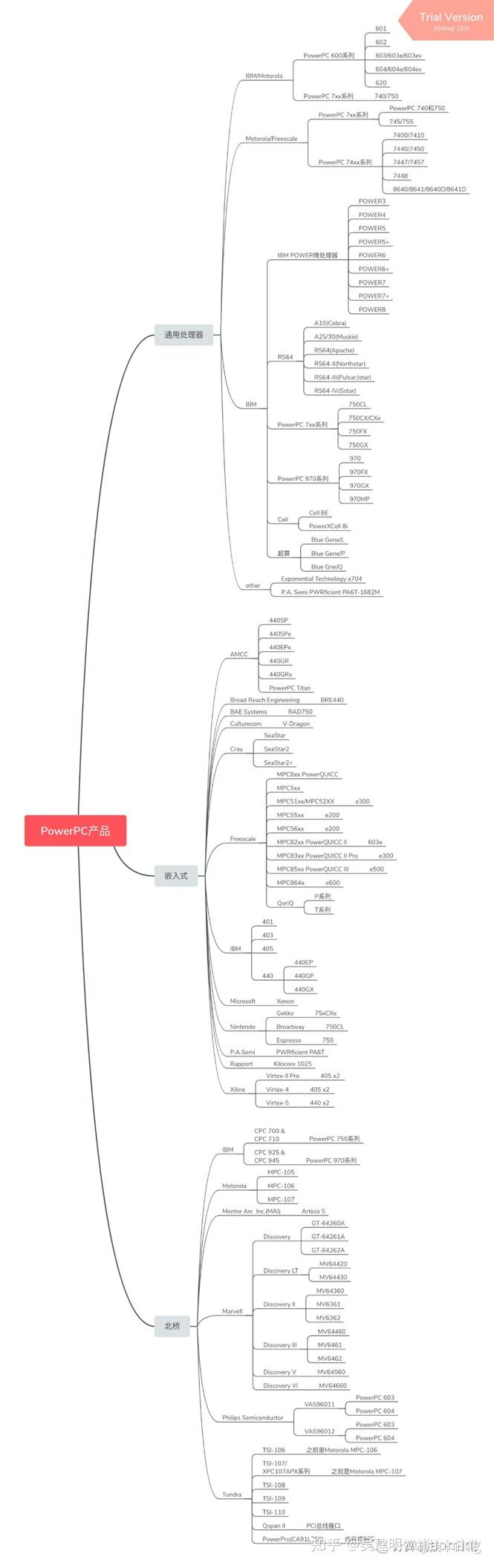

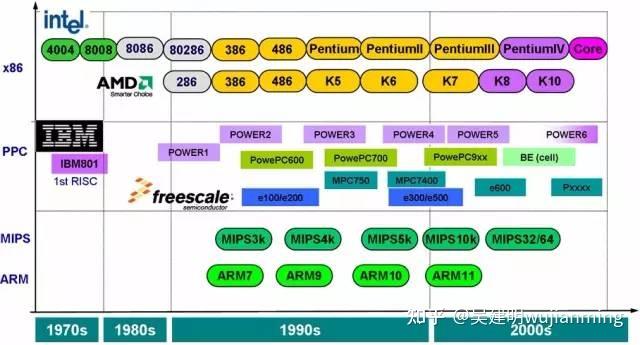

整理这些,是因为PowerPC的产品实在太复杂。比较ARM,x86以及PowerPC:ARM系列产品虽然众多,但是该系列的内核版本变化一目了然。x86系列产品则主要是Intel和AMD,都是自家产品,产品线非常清晰明了。唯有PowerPC,虽然出自IBM,但是经过AIM的分合,IP核的授权,IP在各个公司之间转授还有IBM的回购等等一系列商业活动,除了ISA有着清晰的演化历史,各家产品已经千变万化,完全不是IBM或者Freescale可以控制的了。而PowerPC产品本身也经历了从通用处理器到嵌入式处理器和超算服务器等处理器的转变,从最低端的嵌入式应用(毫瓦级功耗)到最高端的嵌入式应用,从PC(目前居然还有PowerPC的PC产品!)到高端服务器都有用到PowerPC的身影。虽然PowerPC不像ARM或者高通一样主要通过授权来获取收益,但是其IP的授权范围依然很广,各个厂家在其IP上。虽然这些都是PowerPC产品比较复杂的原因,但是最重要的原因还是PowerPC产品有着强大的生命力,其技术先进,背景强硬,历史悠久,用户基础广泛,本应一骑绝尘,走上巅峰,奈何老东家各种奇葩决策,最终导致PowerPC逐渐不被大众所知。

而对来说,在阅读VxWorks for ppc代码的时候,对PowerPC混乱的产品线最直观的体现就是VxWorks中定义的宏。最困惑的一点是使用的CPU到底应该使用哪个宏定义,尤其是目前使用的MPC7448产品,即便整理出以上资料,依然找不到对应的宏定义。

PowerPC介绍

二十世纪九十年代,IBM(国际商用机器公司)、Apple(苹果公司)和Motorola(摩托罗拉)公司开发PowerPC芯片成功,并制造出基于PowerPC的多处理器计算机。PowerPC架构的特点是可伸缩性好、方便灵活。第一代PowerPC采用0.6微米的生产工艺,晶体管的集成度达到单芯片300万个。

随着PowerPC的 发展,使用PowerPC构架的处理器已经形成了庞大的家族,在通信、工控、航天国防等要求高性能和高可靠性的领域得到广泛应用,是一颗“贵族的芯片”。 目前几乎没有什么中文资料详细阐述PowerPC家族谱系,实在是一件遗憾的事。本文就给初学者简介PowerPC家族。

要阐述清楚PowerPC的发展不是一件容易的事情,光是“PowerPC”这个词,就很容易被搞混,尤其是IBM注册了一系列相关的商标。比如Power 、Power PC、PowerPC 这三个词的含义就不止3种,需要工程师聪明的头脑才能区分。一般情况下的PowerPC,指的是使用PowerPC指令集的处理器。

二十世纪九十年代,IBM(国际商用机器公司)、Apple(苹果公司)和Motorola(摩托罗拉)公司共同开发PowerPC处理器。

PowerPC,最初的含义却不是Power,而是Performance Optimized With Enhanced RISC;PC指的是Performance Computing。

目前,主流的PowerPC处理器制造商有IBM、Freescale™ Semiconductor(原摩托罗拉半导体部)、AMCC、LSI等。其中以IBM和Freescale的PowerPC处理器最为流行。本文就以这两家公司的PowerPC处理器为基础,展开讲述PowerPC家族。

IBM的PowerPC家族

IBM目前共有3个主要的PowerPC处理系列

:Power、Power PC和CELL。POWER,POWER PC中间,还有一个Star系列。

POWER系列CPU 从1990开始生产、装备到RS/6000(即RISC System/6000)UNIX工作站和服务器上,现在被称为eServer™ pSeries®服务器(最新的名称是POWER System p系列),主要的型号有POWER 1,POWER 2™,POWER 3™,POWER 4™,POWER 4+,以及目前的POWER 5,POWER 5+和刚刚推出的POWER 6处理器。

最早的801是POWER系列处理器的前身,设计非常简单,为了实现所有的指令都能在一个时钟周期内完成,因此缺乏浮点运算和并行处理能力,POWER架构为了解决这个问题,或者说超越801的限制,增加到了100多条指令,成为一种很“复杂”的精简指令集CPU。

1.POWER 1

发布于1990年,每个芯片大约封装了80万个晶体管。

与 当时其他的处理器不同,POWER 1进行了功能分区,这种设计方案使POWER 1具有非常好的扩展能力,有单独的浮点寄存器,可以适用于从低端UNIX工作站到高端UNIX服务器各种环境。最早的POWER 1是安装在同一母板上的几个芯片的组合,不过很快就集成到一个芯片中,成为单芯片设计,总计拥有超过一百万个晶体管的RISC处理器(RSC,RISC Single Chip,即单芯片的RISC处理器)。POWER 1最成功的应用是被用于火星探路者宇宙飞船上。

2.POWER 2

发布于1993年,每个芯片封装了一千五百万个晶体管。

POWER 2增加了第二个浮点单元处理(floating-point unit,FPU)和更多的缓存。被称为P2SC(Power 2 Scalable Chip)的超级芯片使用CMOS-6S技术,用一个芯片实现了POWER2 8个内核的架构(从这里可以看到其实在1993年IBM就已经开始了多核芯片的设计,其实如果囊括大型机,在20世纪80年代,就有了多核的概念),就 是使用这种处理器的32个节点的DEEP BLUE(深蓝)超级计算机,在1997年战胜了国际象棋冠军卡斯帕罗夫。

3.POWER 3

发布于1998年,每个芯片封装了一千五百万个晶体管。

这 是IBM第一款64位对称多处理器结构(SMP),与原有的POWER指令集完全兼容,也兼容Power PC指令集,主要用于科学计算,从航空设计、生物制药数据分析到天气预测。具有一个数据预取引擎,非阻塞的内置数据缓存和双浮点处理单元。POWER 3-II采用与POWER 3相同的设计,在制造芯片时使用了铜导线技术,在几乎相同的价格制造成本下,提高了一倍的性能。

4.POWER 4

发布于2001年,每个芯片封装了一亿七千四百万个晶体管。

这 是一款达到GHz主频的处理器,0.18微米铜导线,硅绝缘技术。具有POWER 3的全部特性,包括与Power PC指令集兼容,但又是全新的设计,每个处理器包含两个64位1GHz+ Power PC内核,这是业界第一款批量生产的单芯片双核设计,又被称为单芯片对称多处理设计(multicore design on a single die,SMP on a chip,或者system on a chip),每个处理器可以同时执行200条指令。POWER 4架构可以制造IBM Regatta(即p690)大型服务器,也被用来设计Power PC 970处理器(在苹果公司被称为Apple G5)。POWER 4+™(又被称为POWER 4-II)是POWER 4主频升级的提高版。POWER 4 CPU支持了分区技术,可以将芯片切分成多个单元,运行不同的操作系统。

5.POWER 5 ™

2004 年发布,与POWER 3和POWER 4类似,POWER 5同时使用了POWER和Power PC架构,利用了更快的片内通信技术、芯片多处理技术、同时多线程技术(simultaneous multithreading,SMT,一个物理CPU内核可以模拟两个逻辑CPU,如果两个线程的工作内容相差较大,则使用SMT技术性能最高可以达到 单个CPU方式执行的1.5~1.7倍),比POWER 4性能提高了4倍。POWER 5的高端服务器代号为“骑兵队”(“Squadrons”,IBM希望此CPU能如同骑士马队冲锋一样横扫UNIX服务器市场,结果似乎应验了设计者的期 望)。在POWER 5上支持了微分区(Advanced Virtualization)的功能,可以将一个处理器内核虚拟切分成多个处理器,供操作系统使用,最小的分配粒度为0.1个CPU,共享使用粒度是 1/100个CPU。在2006年,IBM推出了主频提高,封装变化的POWER 5,被称为POWER 5+,最高主频为2.2GHz。

6.POWER 6 ™

在 2007年5月发布,目前最高主频4.7GHz,最高明年将有超过5GHz主频的版本。片内集成度约为7亿5千万个晶体管。POWER 6将一些总线控制和CPU内核之间的数据通道集成进单一芯片,与POWER 5相比,增加了更多的CPU内核间通信机制和Cache。POWER 6比较有特点的技术是可以直接支持10进制数字处理,这是计算机史上的一次回归,从十进制转到二进制以便于计算机处理,而如今,计算机芯片设计已经足 够先进,让可以不再去适应机器,而是让机器适应需求。

POWER 6其他的技术包括双核,128KB的L1 Cache(数据、指令各64KB),8条两阶流水线支持在一个时钟周期完成两组32位读或一组64位写操作;两个内核各有4MB“半共享”的L2 Cache,虽然被一个内核占据,但另一个内核也可以快速访问;另外32MB的L3 Cache可被两个内核通过80GB/s的带宽访问;POWER 6还通过ViVA-2(VirtualVector Architecture)技术提高了向量处理性能;支持最多1024个虚拟分区也是POWER 6的新特点(POWER 5最多支持256个分区)。POWER 6特有的10进制运算寄存器、指令可以使在计算时不会产生2-10进制转换误差,同时也提高了运算速度。POWER 6包括一些额外的电路去支持Mainframe的指令,开始了整合z系列的实践,而POWER 6L则是“简化”版的芯片,降低了主频,可以用于刀片服务器。

在生产POWER 6的同时,POWER 7也处于紧张开发阶段,预计2012年面世。

IBM Power 7处理器采用了IBM的45nm SOI铜互联工艺制程,典型的Power 7处理器具有八个核心,提供4核、6核、8核心型号,晶体管数量达到了12亿,核心面积567mm2,从这里可以明显看出Power7的与众不同,作为对比,同样八核心的Nehalem-EX具有23亿个晶体管,整整多了一倍。

| 上市年份 | 2010 |

| 设计厂商 | IBM |

| 最高设计频率 | 2.4 GHz 至 4.25 GHz |

| 制造工艺 | 45 nm |

| 指令集构架 | Power ISA v2.06 |

| 核心数 | 4, 6, 8 |

| L1缓存 | 32+32 KB/core |

| L2缓存 | 256 KB/core |

| L3缓存 | 32 MB |

8核5GHz RISC处理器新代表IBM Power7+

在服务器市场,代表开放性架构的x86服务器尽管在销量上可占到总体的80%,但市场分额只能保持在50%上下,原因在于企业关键业务上,小型机向来都是首选。小型机,一种介于PC服务器和大型机之间的高性能计算机,一般认为,传统小型机是指采用RISC、MIPS等专用处理器,主要支持UNIX操作系统的封闭、专用的计算机系统,所以又称RISC服务器或Unix服务器。不久前,IBM发布了其最新的RISC处理器Power7+。

IBM在8月底的时候公布的Power7+处理器结构,同时还发布了采用Power7+的大型机zEnterprise EC12,现在采用Power7+处理器的服务器也将在10月3号首次问世,Power7+作为32nm制程工艺的IBM最新Power架构处理器,有8个核芯,主频超过5GHz。

自从1993年Power1问世以来,Power架构已经有将近20年的历史。基本上是每三年更新一代,IBM也凭借着Power架构处理器,逐渐开拓Unix服务器市场。

凭借这Power架构处理器这柄利器,IBM在Unix服务器(小型机)市场的华山论剑中力拔头筹。下图是权威咨询机构IDC 09年5月公布的关于小型机市场份额的数据图。

从图中可以清楚的看到随着Power4/5/6的发布,IBM的份额是节节高升。曾长期占据主导地位的Sun和惠普现在被IBM超过,根据权威咨询机构Gartner和IDC的统计数据,2009年第三季度,IBM在Unix服务器市场占据40%的份额,其次分别是惠普(30%)和Sun(不少于25%)。IBM、HP和Sun在小型机市场形成了三国鼎立之势。

凭借着Power架构系列处理器的强劲表现,IBM在小型机上超过了曾长期占据主导地位的惠普和Sun。>>

8月28号,在硅谷举行的Hot Chips 24 芯片大会上,IBM芯片领域的专家介绍了Power架构的最新一代处理器8核Power7+。IBM zEC12采用的IBM Power 7+处理器,主频高达5.5GHz,而核心数也确定为6个。

最新的Power7+处理器采用的是32nm制程工艺,8核芯架构,此次Power7+处理器的发布,吻合了IBM Power架构处理器每三年更新一代,且在两代之间的X+发布的规律。

此前的Power7是在2010年2月8号发布的,IBM在纽约正式发布其Power7处理器。

典型的Power7处理器是单晶片的,具有八个核心,另外也提供4核与6核型号。晶体管数量为12亿,核心面积567mm2。采用的是IBM的45nmSOI铜互联工艺制程。

Power7处理器共有三级缓存,同时还集成了两个四通道DDR3内存控制器,持续内存带宽100GB/s,每个通道的速度为6.4Gbps,最大可以访问32GB(使用两根16GB内存条)。Power7处理器最大可以访问256GB。SMP带宽360GB/s,整个芯片总带宽高达590GB/s。

从Power7到Power7+,最大的变化在于制程工艺从45nm提升到了32nm,在向上扩展(scale up)和向外扩展(scale out)上都有提升。

向上扩展上,虽然Power7+还是和Power7一样是8核芯架构,但是主频提高了不少,虽然IBM没有正式给出Power7+的主频数据,但是由于制程工艺从之前的45nm提升到32nm,有专业人士分析称Power7+的主频相比Power7提升了25%左右。大部分Power7处理器的主频在3GHz到4GHz,而据报道称Power7+处理器的主频则是在5GHz以上,之前有消息称应用在IBM最新大型机的Power7+主频高达5.5GHz。

除了在主频上的提升外,Power7+的L3缓存有提升,是Power7的2.5倍,此前Power7处理器中8个核芯共享25MB的三级缓存。在Power7+中,共享的L3缓存增加到了80MB,大约是此前的2.5倍。

而在横向的向外扩展上,Power7+注重了带宽上的考虑,此前在Power7处理器中,有一个QCM(quad-chip module)模式,就是将4个8核芯的Power7封装在在一起,而在Power7+中,同样有这种模式,只不过将原来封装在一起的四个处理器改为了两个,也就是DCM(dual-chip module)模式。

这种将多个处理器封装在一起的好处是能够提供高系统I/O带宽。提供系统等的性能。从上图对比可以,单处理器的Power7+相比于Power7性能上有30%左右的提升,而DCM模式的Power7+相比于Power7则是有接近50%的性能提升。>>

首批采用Power7+处理器的是IBM大型机zEnterprise EC12,而不久前,IBM宣布将会在10月3日发布采用Power7+的RISC服务器。

目前IBM的RISC服务器采用的处理器多为Power7。IBM实际上在2011年2就宣布停产Power6和Power6+处理器,基于这些处理器的产品也将陆续停止出售。

在2006年2月的国际固态电路会议(ISSCC)上,IBM 公布了Power6处理器,那年10月的微处理器论坛和次年2月的ISSCC上披露了更多细节,最终在07年5月24日于北京召开的“Power6大突破,创"芯"世界”新闻发布会上正式发布了这款取代Power5+的新一代处理器。

有小幅改进的Power6+处理器是在2009年4月正式公布的,但实际上在08年10月发布的Power 560和570系统已经运用了Power6+处理器。从Power3起,IBM每三年发布新一代的Power处理器,而在这三年中间又会发布X+处理器,Power7于2010年2月正式发布,Power7+处理器则是在2012年9月发布。

Power 7+ 派生处理器

第一个PowerPC处理器PowerPC 601,基本上是一个部份基本指令用微码模拟的RSC处理器,采用了Motorola 88000为基础的总线设计。这允许IBM在许多任务作站机器上使用这个处理器,只需要更换主板。自此 PowerPC和POWER架构有些许分岐,但大部份在指令层级仍然保持兼容。

使用在太空应用的抗辐射设计RAD6000处理器是一个POWER/RSC的派生架构。

IBM RS64家族处理器根基于PowerPC(因此也包括POWER),使用在RS/6000和AS/400产品线。对商用工作优化,没有POWER产品线应有的浮点运算。被POWER4取代。

IBM Gekko处理器是修改过的PowerPC 750CXe,使用在任天堂Gamecube。任天堂的Wii使用更新的Gekko,Broadway。

Cell处理器也是从POWER架构派生。具有一个复杂的多线程超标量核心,和称作SPE (Synergistic Processing Elements)的八个独立矢量处理器核心。这个处理器支撑了Sony的Playstation 3、Toshiba的数字电视系统,和IBM的高性能电脑。

微软最新一代的游戏主机Xbox 360使用一个循序运行的三核Xenon处理器,基于PowerPC,拥有修改过的矢量单元,时钟频率3.2 GHz。

Star系列处理器

,是Power PC架构的另一种技术实现,与POWER系列非常类似。由于此系列的各种CPU代号都有Star或者用某一颗星的名字来命名,因此被称为Star系列。

1.RS64

1997年发布,代号为“Apache”。

这 一系列使用Power PC处理器设计,继承了大量POWER架构的特点,但为了商业运算进行了特别优化,与POWER 3相比,其中包括指令分支预测、浮点意外处理、硬件预取等功能被取消,而取而代之的是整形计算意外处理、复杂的片内/片外缓存算法、更大的缓存容量。 RS64的设计可以支持64位处理,在2000年发布的RS64 IV中采用了硬件多线程技术,单台服务器最多可以扩展到24颗CPU,消耗的功耗也非常少,每个处理器只有15瓦。此款CPU开始用于AS/400(即后 来的iSeries),从RS 64 II起,才用于RS/6000(pSeries)。

这种设计使得RS64芯片比较适用于在线交易 (On-Line Transaction Processing,OLTP)、企业资源计划系统(Enterprise Resource Planning,ERP),以及其他大型、混合的多功能、数据库访问、多用户、多进程的业务。不过在实际使用的过程中,发现其计算速度稍有欠缺,可能是 RS64 CPU的主频都很低,典型的几款服务器主频只有100MHz左右,对于商业智能(Business Intelligence,BI)和科学计算一类的应用,性能不佳。

2.RS64 II

1998年发布,代号为:“Northstar”(北方之星)。

该CPU拥有8MB L2 Cache,256位的数据总线,262MHz主频。装配此款CPU的服务器可以支持最多三个CPU板,每个CPU板装载4路CPU,这样可以使RS/6000服务器具有4路、8路、12路的SMP结构。

3.RS64 III

1999年发布,代号为:“Pulsar”(脉冲星)。

第 一款使用硅绝缘的RS64芯片,通过6个CPU 卡可以实现24路SMP结构。由于此款CPU主频提高到450MHz,使用优化的指令分支预取技术避免了跳转惩罚(或只需要额外1个时钟周期),5级流水 线等技术,CPU处理性能大幅度提高。IBM用此款服务器装配了RS/6000的80系列(H80,M80,S80服务器)。

4.RS64 IV

2001发布,代号为:Istar,SStar

第一款支持硬件多线程的商用处理器,比以前同系列的CPU更快,更小。600-750MHz的主频,硬件多线程技术(HMT)使得此CPU具有不错的市场表现。另外每个CPU仅消耗15W的功率也使得用此CPU装配的服务器无需特别的电源、散热系统。

由于市场对于商业和计算环境的混合需求,使得IBM重新整合了POWER系列和Power PC系列处理器,最终设计了POWER 4处理器。Star系列也最后完成了历史使命。

Power PC系列

,是从POWER架构发展出来的一个分支,最早在1993年发布,用于从单板机、电池电源管理到超级计算机和Mainframe主机。Power PC最早登上主角的地位是从作为Power Macintosh 6100的CPU开始的。

众所周知,Power PC开始与苹果、摩托罗拉和IBM联盟(被称为AIM联盟),是源自于POWER架构的设计,但进行了大量的改动。例如,Power PC是open-endian设计,即同时支持大尾段(big-endian)和小尾段(little-endian)内存模式,而POWER 是大尾段设计;Power PC希望提供更强的浮点处理能力和多线程处理能力。所以这两种类型的CPU并没有太大的差别,Power PC保留了绝大部分POWER指令,许多应用只要重新编译,就可以分别在两个平台上运行。

当IBM和摩托罗拉分别自己设计芯片的时候,依然遵循统一的标准。在2000年,大家使用的是Book E spec,这个设计实现使Power PC能更专注于嵌入式处理系统,例如网络、存储和家用设施的处理器。

除了兼容之外,Power PC的架构的另一个亮点是开放,公开了指令集,允许任何厂商设计Power PC的兼容处理器、Power PC的一些软件的源代码也可以下载到,Power PC的内核也非常小,可以在同一芯片上安置许多其他的辅助电路,例如缓存、协处理器,大大增加了芯片的灵活性。

IBM四条服务器产品线中有两条都与Power PC架构有关,另外苹果公司的台式机和服务器、任天堂的GameCube,IBM自己的蓝色基因超级计算机都使用了PowerPC芯片。

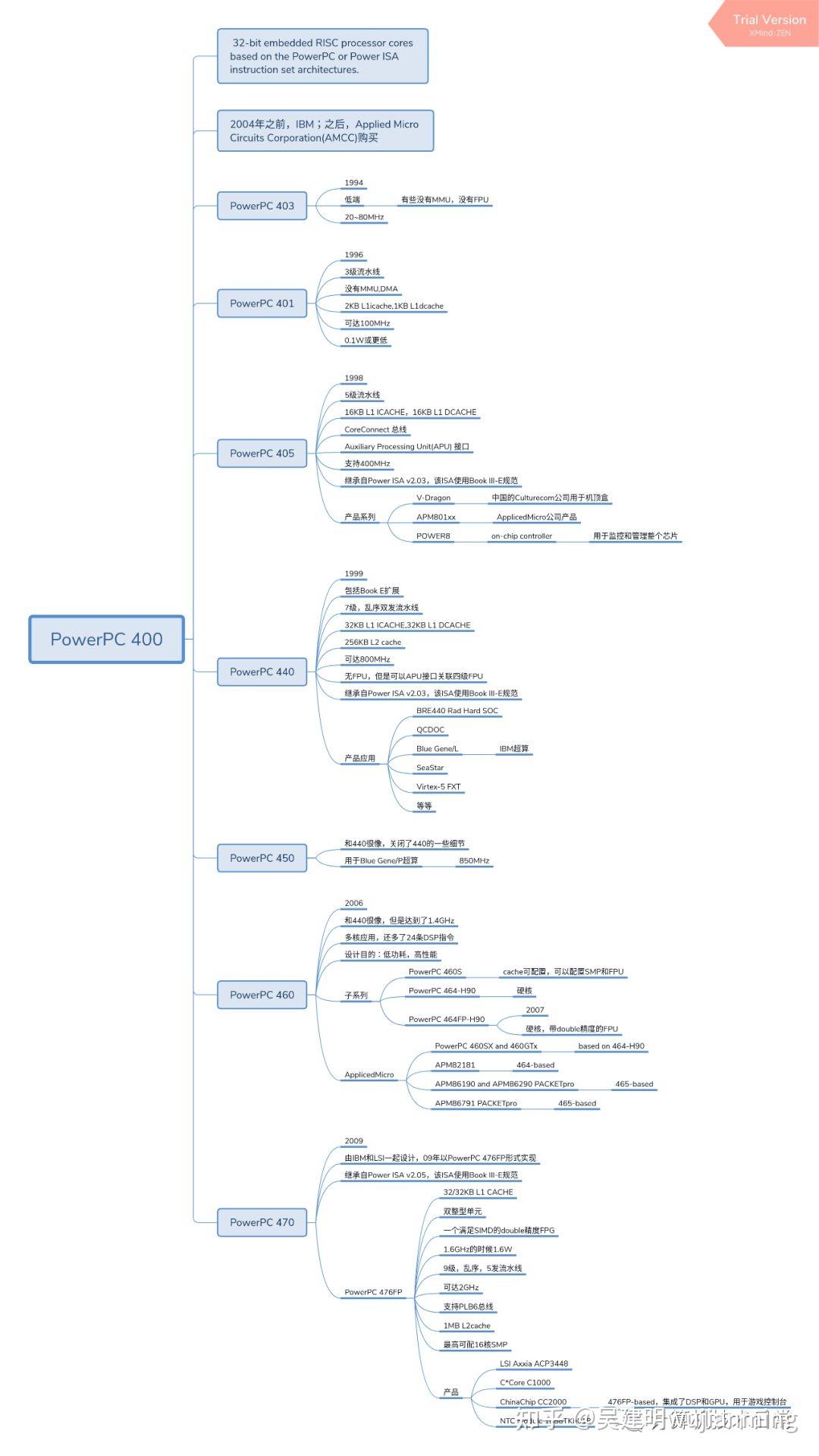

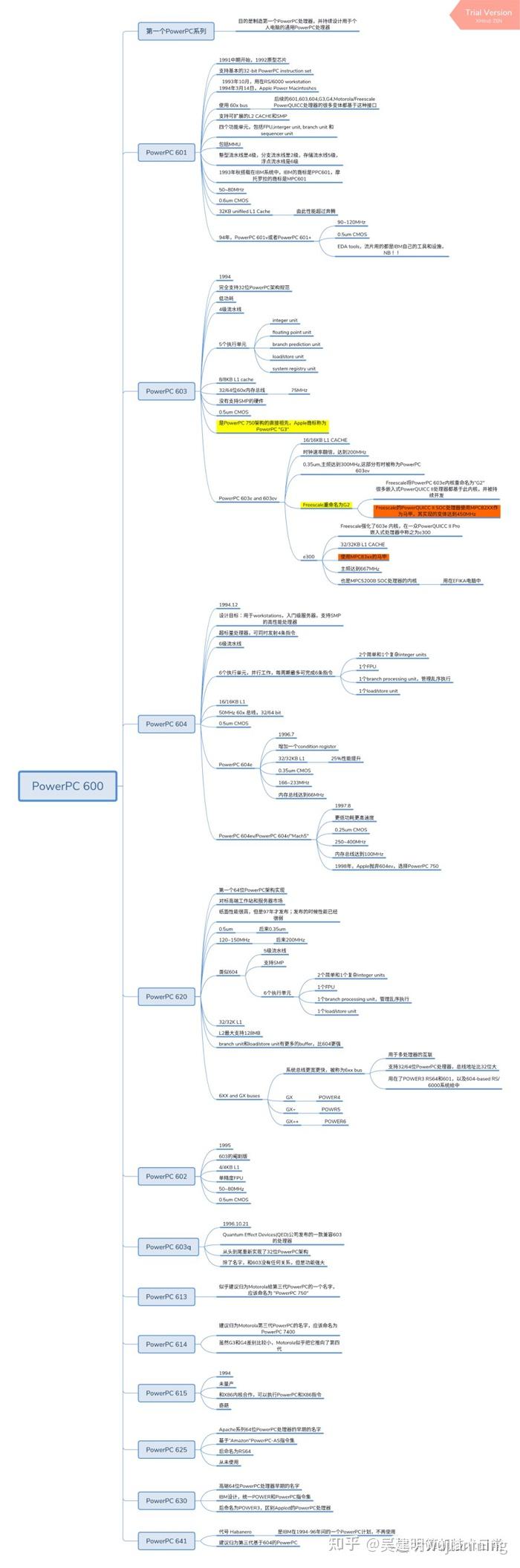

今天,Power PC家族有三条产品线,分别是嵌入式的Power PC 400系列,Power PC 700和Power PC 900系列。从历史上看,还有一款Power PC 600系列最值得关注,因为具有非常好的性能。

1.Power PC 600系列

Power PC 601是Power PC 600系列中的第一款,综合了POWER和Power PC架构的特点,并且尽量保持与POWER 1和随后的其他Power PC芯片的兼容性(即使是同一系列的芯片,也存在兼容性问题),甚至与摩托罗拉的88110兼容。苹果公司用Power PC 601在1994年制造了Power Mac 6100,66 MHz CPU主频。此系列下一个芯片是603,低端、低功耗的处理器,大量使用在汽车上。与Power PC 603®同日登场的还有PowerPC 604®,是更强大的处理器,随之的是“加强版”的603e和604e。在此之后,第一款64位Power PC——Power PC 620®在1995年被发布。

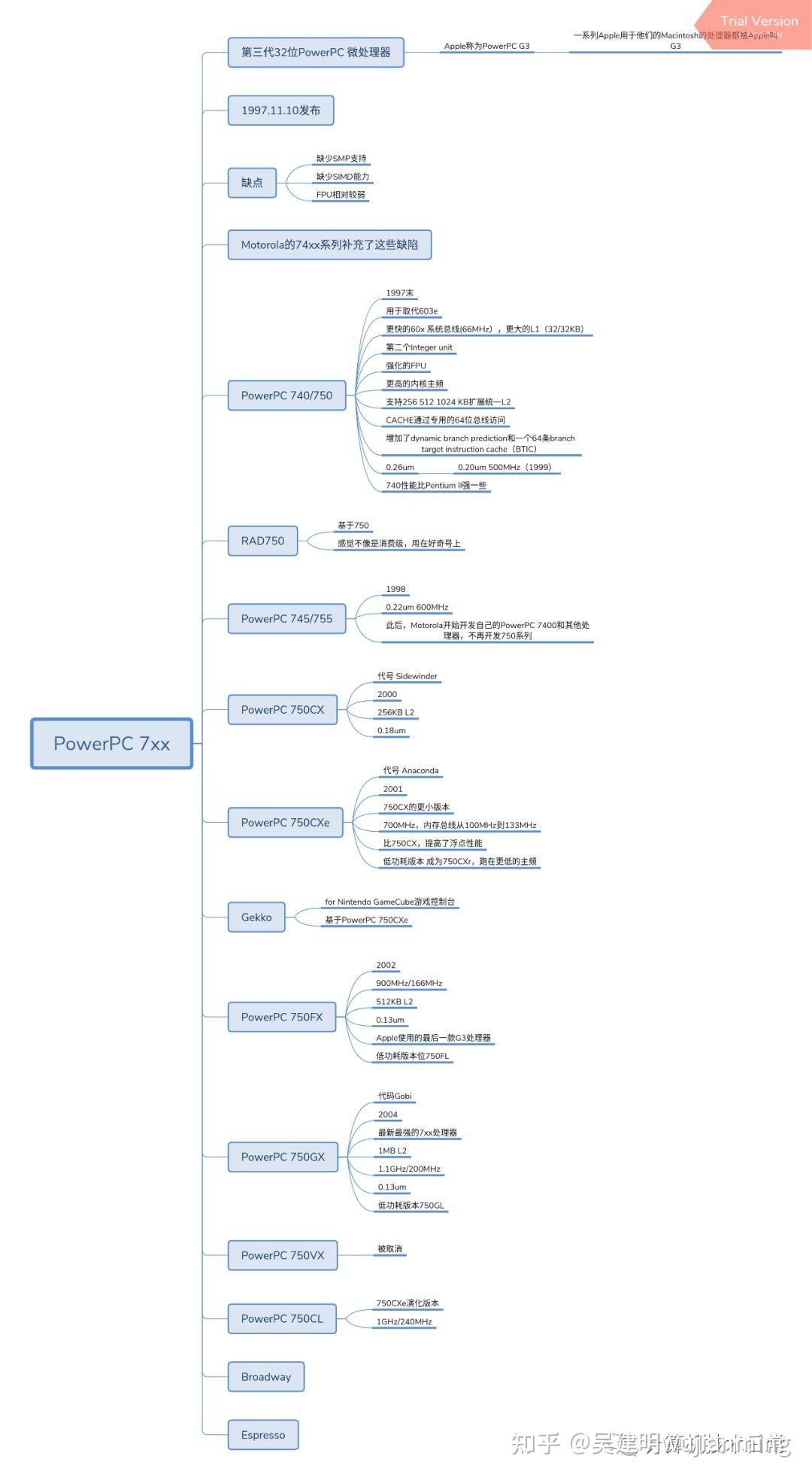

2.Power PC 700系列

在 1998年,出现了Power PC 740和Power PC 750,与604e非常相像,甚至一些人说600/700两个系列根本就是一回事。Power PC 750是第一款铜导线处理器,苹果公司用生产了G3,但很快就被G4所取代,使用的是摩托罗拉7400。在2002年发布的32位的Power PC 750FX曾经震惊业界,因为是第一款达到1GHz主频的处理器,IBM在2003年紧跟着推出了750GX,集成了1MB片上二级缓存,也是1GHz 主频,大约7瓦功耗。

3.Power PC 900系列

64位的Power PC 970,实际上是单处理器内核的POWER 4,可以同时执行200条指令,最高达到2 GHz以上的主频,而仅仅消耗十数瓦的电力。低功耗使被大量用于笔记本电脑和手持设备上,还有一些高密度的存储、服务器(例如刀片中心)也在使用。 64位处理能力,单指令多数据流设计使更适合于多媒体、图形处理。苹果公司的台式机、Xserve服务器,以及其他一些图形、网络设备,都在使用这款处 理器。例如苹果Xserve G5就使用了Power PC 970FX,也是第一款同时使用了应变硅、硅绝缘两项技术的芯片。

4.Power PC 400 系列

这 一款芯片主要用于嵌入式系统,但Power PC灵活的架构使可以被用于从机顶盒这样的小设备到蓝色基因超级计算机。在产品线的一端,Power PC 405EP在200MHz主频仅消耗1瓦的电力,而铜导线的Power PC 440在800 MHz主频可以提供同类型嵌入式芯片中最高的性能。这款芯片也有许多旁支,例如利用Power PC 440GX的双Gigabit Ethernet和TCP/IP加速功能可以降低网络应用程序50%以上的负载。围绕Power PC 400内核,有许多具体实现,用于建造蓝色基因超级计算机的处理芯片就是包含了两个Power PC 440处理器内核和两个浮点处理内核。

Power PC 400系列被IBM转让给AMCC,发展成为PowerPC 405 Family、PowerPC 440 Family、PowerPC 460 Family 3大系列。

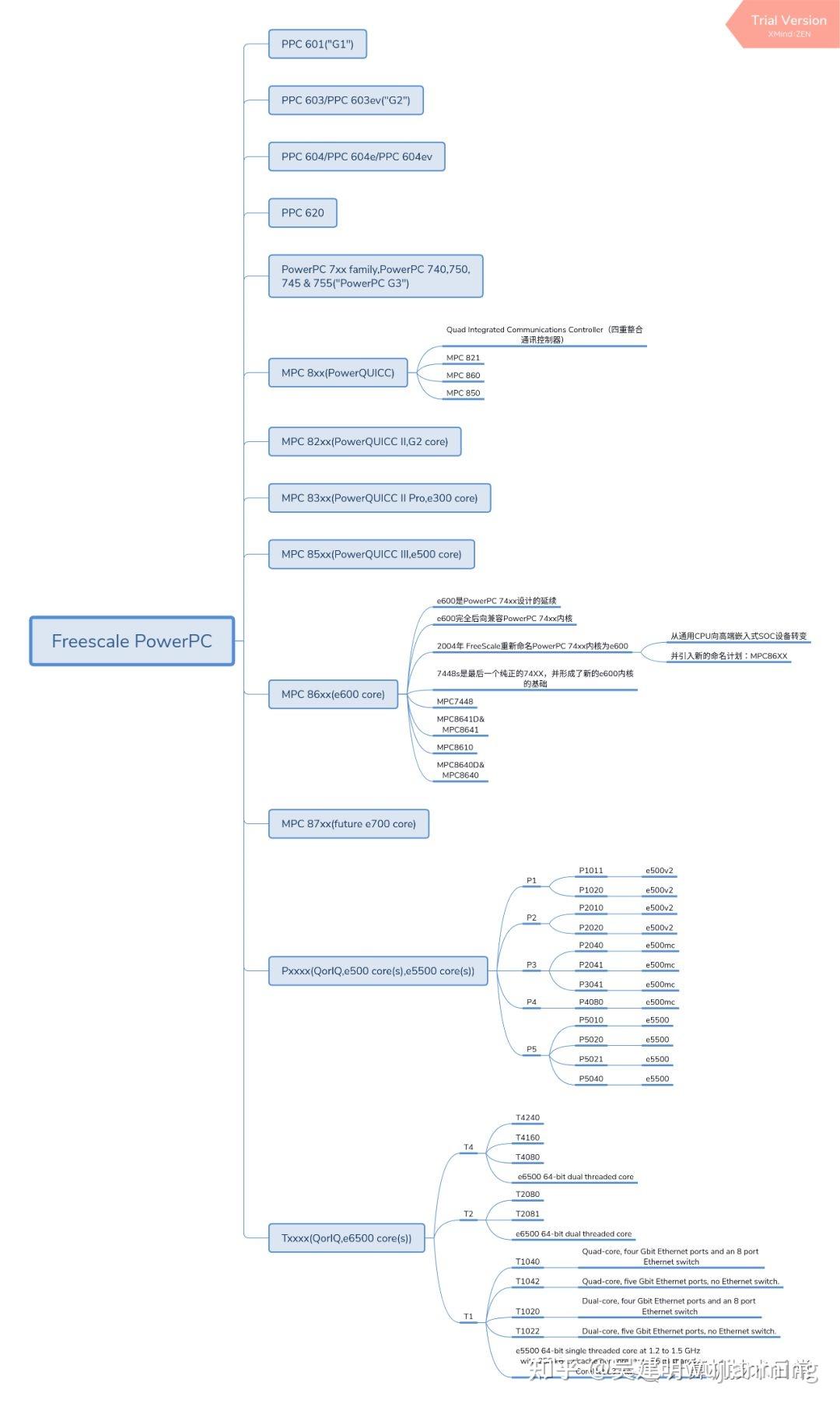

Freescale PowerPC系列

Freescale公司提供了数量众多的含集成化外设的PowerPC处理器,目前在网络设备市场取得了非常可观的成功。目前Freescale公司已经调整其PowerPC产品策略,将其划分成3个主要市场:网络设备、汽车电子(MPC5xx系列)和工业控制。

Freescale PowerPC在通讯领域的成功,很可能要归功于PowerQUICC,这也是IBM的PowerPC和Freescale 的PowerPC的最重要的区别。1993年,摩托罗拉半导体事业部(飞思卡尔半导体前身)在充分理解通信系统应用的基础上,生产了第一颗包含QUICC(Quad Integrated Communications Controller)的芯片--MC68360。此时,QUICC实际上是一颗独立的处理器。1994年,摩托罗拉半导体事业部的工程师开始把MC68360的QUICC和PowerPC内核结合,将集成了QUICC的PowerPC处理器称为PowerQUICC,并将其中的QUICC处理模块称为CPM。

1995年,MPC860芯片面市,标志着一个通信处理器时代的开始。这颗芯片实现了作为控制中心的PowerPC处理器和作为数据处理中心的CPM的分离,采用了数据通路和控制通路分开的思想。

此后PowerQUICC系列芯片也一路升级,从PowerQUICC I到PowerQUICC II,再到PowerQUICC III和PowerQUICC II pro。目前,Freescale 将CPM升级为QE(QUICC Engine)。

伴随PowerQUICC的升级,Freescale PowerPC内核也在升级。

603内核系列:MPC850、MPC860、MPC875、MPC885等,目前是最低端的Freescale PowerPC处理器。这类PowerPC处理器没有包含SDRAM接口,用户必须使用MPC860提供的UPM(USER Programmable Machines)配置成SDRAM接口。603内核配合PowerQUICC I。

603E内核系列:MPC8250、MPC8260、MPC8272等。从PowerPC内核的角度看,603到603E的升级不大,主要是MMU上,此外包含了SDRAM控制器。603E内核配合PowerQUICC II。

E300内核系列:MPC8349、MPC8347、MPC8360等。E300系列与603E系列结构基本一致,在处理器内核上的修改不多。QE最先在MPC8360上实现,此外支持DDR SDRAM接口。E300内核配合PowerQUICC II pro。

E500内核系列: 包括MPC8540、MPC8560、MPC8548等。E500内核共有V1 、V2两个版本。V1版本和V2版本的最大区别在于MMU。基于E500内核的PowerPC处理器是Freescale高端处理器的发展方向。E500 内核和603E有很大的不同,只有指令系统是兼容的,其他内核组件都不相同。E500内核支持DDR SDRAM,RapidIO和千兆以太网接口。E500内核配合PowerQUICC III。

E600内核系列:也称为G4,包括MPC7410,MPC7447,MPC7448,MPC8641等。与IBM的Power 700系列的最大不同在于G4系列支持AltiVec结构。这类处理器也是Apple用于MAC机的芯片。

E700系列:支持64位的PowerPC结构,开发中(最新消息不明,怀疑被放弃).

飞思卡尔 QorIQ通信平台是飞思卡尔的 PowerQUICC通信处理器的下一代演进产品,包含一个或者更多个核,一共有5个不同的产品平台。按照功能和性能,分为 P1, P2, P3, P4 和P5,同老的PowerPC产品保持软件兼容,例如PowerQUICC平台。

QorIQ 商标和P1、P2、P4产品家族在2008年6月被公布,P3和P5平台的细节尚未公开。所有的QorIQ处理器基于 e500 or e5500 核心。P10xx 和 P20xx 系列基于e500v2 核心,P340xx 和P40xx 系列基于 e500mc 核心,P50xx 则基于e5500 核心。

P1系列

P1系列被设计用于网关、以太网交换机、无线局域网接入点和通用控制目的。P1系列属于入门级,运行在400到800MHz,用于替代PowerQUICC II Pro 和PowerQUICC III平台。P1系列封装成689个引脚,同P2系列兼容。

P1011 -包含一个800MHze500核心,256 kB L2 cache,4个SerDes lanes,3个吉比特以太网控制器,以及一个用于老实电话的时分复用引擎(TDM engine) 。

P1020 –包含2个800 MHz e500 核心,256 kB shared L2 cache, 4个SerDes lanes,3个吉比特以太网控制器,一个 TDM engine.

P2系列

P2系列设计用于网络、电信、军工的广泛应用。能运行在-40 到 125 °C,特别适合苛刻条件下的应用。P2系列属于中端产品,运行在800Mhz到1.2GHz,用于替代PowerQUICC II Pro 和PowerQUICC III平台。

P2010 – 包含1个 1.2 GHz 核心

P2020 – 包含2个 1.2 GHz 核心, shared L2 cache

P3系列

P3 系列设计属于中端产品,用于交换机和路由器。P3系列提供了一个多核平台,支持4个e500mc核心,每个核心频率能达到1.5 GHz。P3系列拥有1.3 GHz 64-bit DDR3内存控制器,18个SerDes lanes,以及用于数据包操作和调度、正则表达式、RAID、安全、加密和RapidIO的硬件加速器。

P3系列的多个核心能够运行在对称模式和非对称模式,意味着多个核心可以一起或者非别引导运行操作系统。

P3041 - 4个1.5 GHz 核心,每个核心128 kB L2 cache ,1个1.3 GHz 64-bit DDR3 内存控制器,45纳米技术和仅有12w的功率。

P4系列

P4系列属于高端产品,用于核心网或者企业级交换机、路由器。提供极限多核平台,支持8个e500mc核心 ,每一个核达到1.5 GHz。

P4080 –包含8个e500mc核心,每个核心有32/32kB instruction/data L1 caches以及1个a 128 kB L2 cache。包含2个1 MB L3 caches,每一个连接到64-bit DDR2/DDR3 内存控制器。

P5系列

P5系列基于高性能64-bit e5500 核心,频率提高到2.5 GHz 。

P5010 - 一个e5500 2.2 GHz核心, 1 MB L3 cache, 1个DDR3 controller,45 nm 工艺,功率30W.

P5020 - 两个e5500 2.2 GHz核心, 2个1 MB L3 caches, 2个DDR3 controllers, 45 nm 工艺,功率30W.

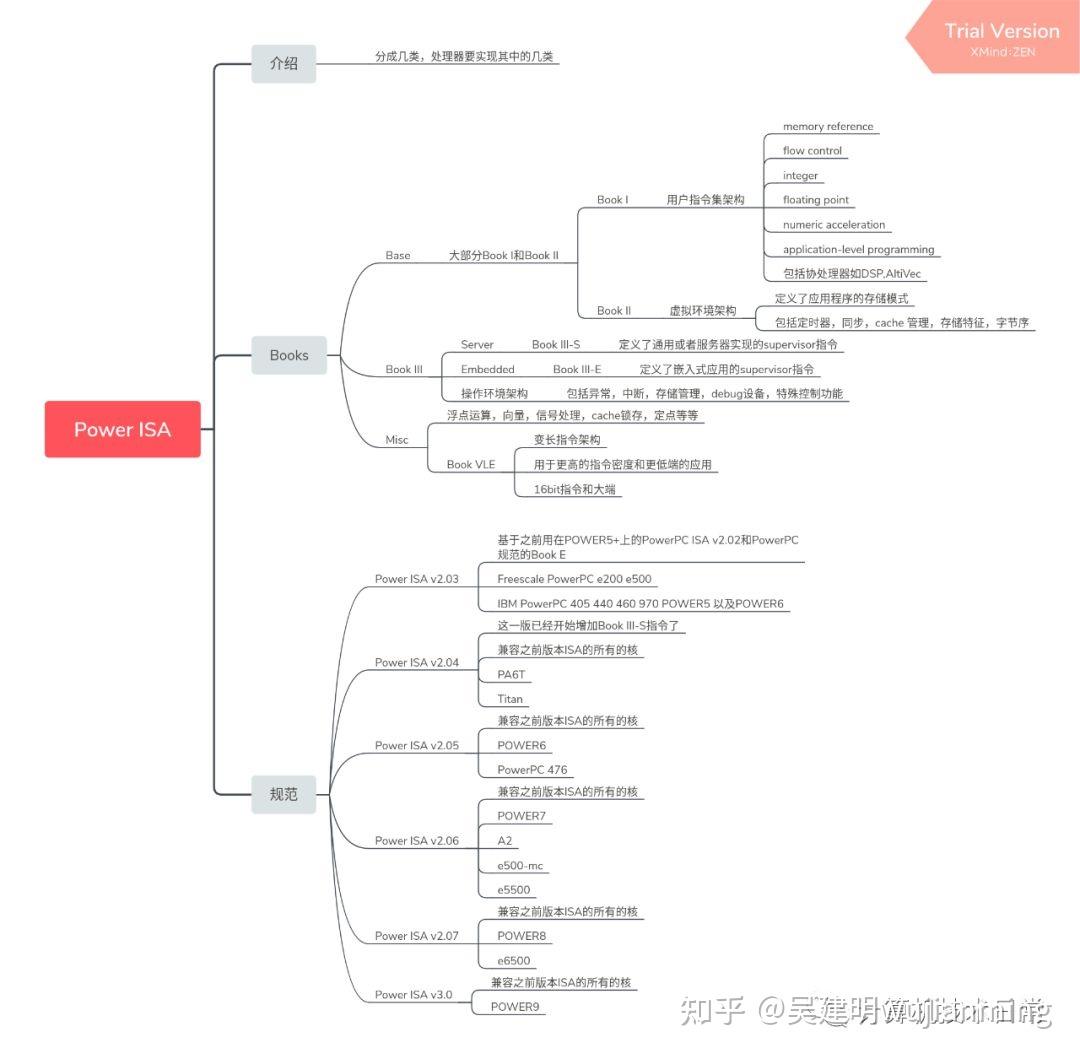

PowerPC指令集

对 PowerPC 体系结构家族树的所有分支来说,PowerPC 体系结构和应用级编程模型是通用的。要获得详细的资料,请参阅 IBM® PowerPC Web 站点技术库中的产品用户手册(参阅 参考资料以获取链接,点击“原文链接”获得更多资料)。

PowerPC 体系结构是一种精减指令集计算机(Reduced Instruction Set Computer,RISC)体系结构,定义了 200 多条指令。PowerPC 之所以是 RISC,原因在于大部分指令在一个单一的周期内执行,而且通常只执行一个单一的操作(比如将内存加载到寄存器,或者将寄存器数据存储到内存)。

PowerPC 体系结构分为三个级别(或者说是“book”)。通过对体系结构以这种方式进行划分,为实现可以选择价格/性能比平衡的复杂性级别留出了空间,同时还保持了实现间的代码兼容性。

· Book I. 用户指令集体系结构

· 定义了通用于所有 PowerPC 实现的用户指令和寄存器的基本集合。这些是非特权指令,为大多数程序所用。

· Book II. 虚拟环境体系结构

· 定义了常规应用软件要求之外的附加的用户级功能,比如高速缓存管理、原子操作和用户级计时器支持。虽然这些操作也是非特权的,但是程序通常还是通过操作系统调用来访问这些函数。

· Book III. 操作环境体系结构

· 定义了操作系统级需要和使用的操作。其中包括用于内存管理、异常向量处理、特权寄存器访问、特权计时器访问的函数。Book III 中详细说明了对各种系统服务和功能的直接硬件支持。

从最初的 PowerPC 体系结构的开发开始,就根据特定的市场需求而发生分支。当前,PowerPC 体系结构家族树有两个活跃的分支,分别是 PowerPC AS 体系结构和 PowerPC Book E 体系结构。PowerPC AS 体系结构是 IBM 为了满足 eServer pSeries UNIX 和 Linux 服务器产品家族及 eServer iSeries 企业服务器产品家族的具体需要而定义的(参阅 参考资料中的链接以获得更多资料)。PowerPC Book E 体系结构,也被称为 Book E,是 IBM 和 Motorola 为满足嵌入式市场的特定需求而合作推出的。PowerPC AS 所采用的原始 PowerPC 体系结构与 Book E 所采用的扩展之间的主要区别大部分集中于 Book III 区域中。

在这些衍生的体系结构中还有一些适当的应用级扩展,这些扩展大部分与具体应用的场合相关,但是 PowerPC AS 和 PowerPC Book E 共享在 PowerPC 体系结构的 Book I 中定义的基本指令集。虽然三种体系结构主要在操作系统级别上表现出不同,但在很大程度上具备应用级的兼容性。

PowerPC 最初定义了同时对 32 位和 64 位实现的支持,可以让 32 位的应用程序运行于 64 位系统之上。在 IBM pSeries 和 iSeries 服务器上使用的 PowerPC AS 系统现在只提供体系结构的 64 位实现,新的 64 位应用程序和遗留的 32 位的应用程序可以运行于同一个系统之上。PowerPC Book E 体系结构同时有 32 位实现和 64 位实现,64 位实现也完全兼容 32 位 PowerPC 应用程序。这两种体系结构都具备与 PowerPC Book I 指令和寄存器的完全兼容性,同时提供了对内存管理、异常和中断、计时器支持和调试支持等各方面的系统级扩展。

POWER 的自然历史

POWER 和 PowerPC 微处理器有着漫长而传奇的历史,最初是 IBM 801,其后是 POWER、RS64 和 PowerPC 芯片系列(这些并不是线性发展的)。每个芯片家族都对计算世界有自己强有力的影响,从游戏控制台到主机,从数字手表到高端工作站,到处都得到了应用。欲了解全部历史,请阅读“ 人类的 POWER:IBM 的芯片制造历史”。

最初的 PowerPC 体系结构仍是 PowerPC AS 和 PowerPC Book E 的主要组成部分,并仍保持了其完整性,表现出了令人信服的应用级兼容性。

PowerPC 应用程序编程模型

当用到不只一种类型的 PowerPC 处理器时,开发人员应时刻谨记处理器处理内存的方式存在一些差异。

PowerPC 存储模型

PowerPC 体系结构本身支持字节(8 位)、半字(16 位)、字(32 位) 和双字(64 位) 数据类型。PowerPC 实现还可以处理最长 128 字节的多字节字符串操作。32 位 PowerPC 实现支持 4-gigabyte 的有效地址空间,而 64 位 PowerPC 实现支持 16-exabyte 的有效地址空间。所有存储都可以字节寻址。

对于错位数据访问来说,不同的产品家族提供了不同的校准支持,有一些是以处理异常的方式,其他的是通过硬件中的一步或者多步操作来处理访问。

最高位字节在最前(Big-endian)还是最低位字节在最前(little-endian)?

PowerPC、PowerPC AS 以及早期的 IBM PowerPC 4xx 家族大部分是字节排列顺序最高位在最前的机器,这就意味着对半字、字以及双字访问来说,最重要的字节(most-significant byte,MSB)位于最低的地址。各实现对最低位在最前的字节排列顺序方式的支持不同。PowerPC 和 PowerPC AS 提供了最小限度的支持,而 4xx 家族为最低位字节在最前的存储提供了更为健壮的支持。Book E 是字节排列顺序无关的,因为 Book E 体系结构完全支持这两种访问方法。

PowerPC 应用级寄存器

PowerPC 的应用级寄存器分为三类:通用寄存器(general-purpose register,GPR)、浮点寄存器(floating-point register [FPR] 和浮点状态和控制寄存器 [Floating-Point Status and Control Register,FPSCR])和专用寄存器(special-purpose register,SPR)。让来分别看一下这三类寄存器。

通用寄存器(GPR)

用户指令集体系结构(Book I)规定,所有实现都有 32 个 GPR(从GPR0 到 GPR31)。GPR 是所有整数操作的源和目的,也是所有加载/存储操作的地址操作数的源。GPR 还提供对 SPR 的访问。所有 GRP 都是可用的,只有一种情况例外:在某些指令中,GPR0 只是代表数值 0,而不会去查找 GPR0 的内容。

浮点寄存器(FPR)

Book I 规定,所有实现都有 32 个 FPR(从 FPR0 到 FPR31)。FPR 是所有浮点操作的源和目的操作数,可以存放 32 位和 64 位的有符号和无符号整数,以及单精度和双精度浮点数。FPR 还提供对 FPSCR 的访问。

注意,嵌入式微处理器实现时经常不提供对浮点指令集的直接硬件支持,或者只是提供一个附加浮点硬件的接口。很多嵌入式应用程序很少或者根本不需要浮点算法,而当需要的时候,对 PowerPC 浮点指令执行进行软件仿真就足够了。在嵌入式微处理器中,硬件中省去浮点(支持)而为实现带来的芯片面积和功率的减少是至关重要的。

浮点状态和控制寄存器(FPSCR)捕获浮点操作的状态和异常结果,FPSCR 还具有控制位,以支持特定的异常类型和对四种舍入模式之一的选择。对 FPSCR 的访问要通过 FPR。

专用寄存器(SPR)

SPR 给出处理器核心内部资源的状态并对其进行控制。不需要系统服务的支持就可以由应用程序读写的 SPR 包括计数寄存器(Count Register)、链接寄存器(Link Register)和整型异常寄存器(Integer Exception Register)。需要系统服务的支持才可以由应用程序读写的 SPR 包括时基(Time Base)和其他各种可能支持的计时器。

·

指令地址寄存器(Instruction Address Register,IAR)

这个寄存器就是程序员们所熟知的

程序计数器

或者

指令指针

。是当前指令的地址。这实际上是一个伪寄存器,用户只能通过“branch and link”指令才能直接使用这个寄存器。IAR 主要是由调试器使用,显示将要被执行的下一条指令。

·

链接寄存器(Link Register,LR)

这个寄存器存放的是函数调用结束处的返回地址。某些转移指令可以自动加载 LR 到转移之后的指令。每个转移指令编码中都有一个 LK 位。如果 LK 为 1,转移指令就会将程序计数器移为 LR 中的地址。而且,条件转移指令

bclr

转移到 LR 中的值。

·

定点异常寄存器(Fixed-Point Exception Register,XER)

这个寄存器存放整数运算操作的进位以及溢出信息。还存放某些整数运算操作的进位输入以及加载和存储指令(

lswx

和

stswx

)中传输的字节数。

·

计数寄存器(Count Register,CTR)

这个寄存器中存放了一个循环计数器,会随特定转移操作而递减。条件转移指令

bcctr

转移到 CTR 中的值。

·

条件寄存器(Condition Register,CR)

这个寄存器分为八个字段,每个字段 4 位。很多 PowerPC 指令将指令的第 31 位编码为 Rc 位,有一些指令要求 Rc 值等于 1。当 Rc 等于 1 且进行整数操作时,CR 字段 0 被设置来表示指令操作的结果:相等(Equal, EQ),大于(Greater Than, GT),小于(Less Than, LT),以及和溢出(Summary Overflow, SO)。当 Rc 等于 1 且进行浮点操作时,CR 字段 1 被设置用来表示 FPSCR 中异常状态位的状态:FX、FEX、VX 和 OX。任何一个 CR 字段都可以是整数或者浮点比较指令的目标。CR 字段 0 还被设置用来表示条件存储指令(

stwcx

或者

stdcx

) 的结果。还有一组指令可以操纵特定的 CR 位、特定的 CR 字段或者整个 CR,通常为了测试而将几个条件组合到同一个位中。

·

处理器版本寄存器(Processor Version Register,PVR)

PVR 是一个 32 位只读寄存器,标识处理器的版本和修订级别。处理器版本由 PowerPC 体系结构过程分配。修订级别由实现定义。需要有特权才能访问 PVR,所以应用程序只能在操作系统函数的帮助下才可以确定处理器版本。

PowerPC 应用级指令集

表 1 列出了不同的指令类别以及每类的指令类型。

表 1. 指令类别

| 指令类别 | 基本指令 |

| Branch | branch, branch conditional, branch to LR, branch to CTR |

| Condition register |

crand, crnor, creqv, crxor, crandc, crorc, crnand, cror,

CR move |

| Storage access | load GPR/FPR, store GPR/FPR |

| Integer arithmetic | add, subtract, negate, multiply, divide |

| Integer comparison |

compare algebraic, compare algebraic immediate, compare

logical,compare logical immediate |

| Integer logical |

and, andc, nand, or, orc, nor, xor, eqv, sign extension,

countleading zeros |

| Integer rotate/shift | rotate, rotate and mask, shift left, shift right |

| Floating-point arithmetic |

add, subtract, negate, multiply, divide, square root,

multiply-add,multiply-subtract, negative multiply-add, negative multiply-subtract |

| Floating-point comparison | compare ordered, compare unordered |

| Floating-point conversion | round to single, convert from/to integer word/doubleword |

| FPSCR management |

move to/from FPSCR, set/clear FPSCR bit, copy FPSCR

field to CR |

| Cache control | touch, zero, flush, store |

| Processor management |

system call, move to/from special purpose registers,

mtcrf, mfcr |

指令解析

所有指令的编码长度都是 32 位。PowerPC 的位编号方式与大部分其他定义相反:第 0 位是最重要的位,第 31 位是最不重要的位。指令首先由一个字段中较高的 6 位进行解码,这 6 位称为

主要操作码(primary opcode)

。其余 26 位包含的字段分别是操作数说明、立即(immediate)操作数以及扩展的操作码(opcode),而且这些还可能是保留的位或字段。表 2 列出了 PowerPC 定义的基本指令格式。

表 2. PowerPC 指令格式

| 格式 | 0 | 6 | 11 | 16 | 21 | 26 | 30 | 31 |

| D-form | opcd | tgt/src | src/tgt | immediate | ||||

| X-form | opcd | tgt/src | src/tgt | src | extended opcd | |||

| A-form | opcd | tgt/src | src/tgt | src | src | extended opcd | Rc | |

| BD-form | opcd | BO | BI | BD | AA | LK | ||

| I-form | opcd | LI | AA | LK |

·

D-form

这一指令格式提供至多两个寄存器作为源操作数,一个立即源,至多两个寄存器作为目的操作数。这一指令格式的一些变种使用部分目的和源寄存器操作数说明符作为立即字段或作为扩展的操作码。

·

X-form

这一指令格式提供至多两个寄存器作为源操作数,至多两个目的操作数。这一指令格式的一些变种使用部分目的和源寄存器操作数说明符作为立即字段或作为扩展的操作码。

·

A-form

这一指令格式提供至多三个寄存器作为源操作数,以及一个目的操作数。这一指令格式的一些变种使用部分目的和源寄存器操作数说明符作为立即字段或作为扩展的操作码。

·

BD-form

条件转移指令使用的是这一指令格式。BO 指令字段指定了条件的类型;BI 指令字段指定了以哪个 CR 位作为条件;BD 字段用作转移位置。AA 位指定了转移是绝对转移还是相对转移。换名话说,转移目标地址是立即字段的值,还是立即字段的值与转移地址的和。LK 位指定了下一个顺序指令的地址是否作为子例程调用的返回地址保存在链接寄存器中。

·

I-form

无条件转移指令使用这一指令格式。由于是无条件的,BD 格式中的 BO 和 BI 字段改变为另外的转移位置,以构成 LI 指令字段。同 BD 格式一样,这一指令格式也支持 AA 和 LK 位。

如前所述,这些指令格式各有其变种。不过,这些格式是对大部分 PowerPC 指令集编码结构的最好描述。

转移指令

PowerPC 为控制流程提供了一组指令,包括:

· 条件和无条件转移指令。

· “递减计数和如果是零或者非零时转移”的能力。

· 绝对转移和相对转移。

· 使用链接寄存器或计数寄存器来指定转移目标地址的转移指令。

所有的转移指令都具备保存后继顺序指令地址的能力,包括到链接寄存器的转移。条件寄存器 32 位中的任意一位都可以指定为条件转移的条件,并可以指定 CR 位是否必须为 0 或 1 时转移条件才成立。

条件寄存器指令

PowerPC 提供了一组用于对 CR 的特定位执行布尔操作和对 CR 字段进行拷贝的指令。允许组合多个转移条件,这样可以减少代价高昂的条件转移的数量。表 3 列出了 PowerPC CR 逻辑指令。

表 3. PowerPC CR 逻辑指令

| 助记符 | 指令名 |

| crand | CR logical and |

| crandc | CR logical and with complement |

| creqv | CR logical equivalent |

| crnand | CR logical not and |

| crnor | CR logical not or |

| cror | CR logical or |

| crorc | CR logical or with complement |

| crxor | CR logical xor |

整数运算指令

很多指令用于执行运算操作,包括 add、substract、negate、compare、multiply 和 divide。很多格式用于立即值、溢出检测以及进位和借位。各实现中 multiply 和 divide 的执行是不同的,因为这些通常是多周期指令。表 4 列出了 PowerPC 整数运算指令。

表 4. PowerPC 整数运算指令

| 助记符 | 指令名 |

| add[o][.] | add [& record OV] [& record CR0] |

| addc[o][.] | add carrying [& record OV] [& record CR0] |

| adde[o][.] | add extended [& record OV] [& record CR0] |

| addi | add immediate |

| addis | add immediate shifted |

| addic[.] | add immediate carrying [& record CR0] |

| addme[o][.] | add to minus one [& record OV] [& record CR0] |

| addze[o][.] | add to zero [& record OV] [& record CR0] |

| divd[o][.] | divide doubleword [& record OV] [& record CR0] |

| divdu[o][.] |

divide doubleword unsigned [& record OV] [&

record CR0] |

| divw[o][.] | divide word [& record OV] [& record CR0] |

| divwu[o][.] |

divide word unsigned [& record OV] [& record

CR0] |

| mulhd[.] | multiply high doubleword [& record CR0] |

| mulhdu[.] | multiply high doubleword unsigned [& record CR0] |

| mulhw[.] | multiply high word [& record CR0] |

| mulhwu[.] | multiply high word unsigned [& record CR0] |

| mulld[o][.] |

multiply low doubleword [& record OV] [& record

CR0] |

| mulli | multiply low immediate |

| mullw[o][.] | multiply low word [& record OV] [& record CR0] |

| neg[o][.] | negate [& record OV] [& record CR0] |

| subf[o][.] | subtract from [& record OV] [& record CR0] |

| subfc[o][.] |

subtract from carrying [& record OV] [& record

CR0] |

| subfe[o][.] |

subtract from extended [& record OV] [& record

CR0] |

| subfi | subtract from immediate |

| subfis | subtract from immediate shifted |

| subfic[.] | subtract from immediate carrying [& record CR0] |

| subfme[o][.] |

subtract from to minus one [& record OV] [&

record CR0] |

| subfze[o][.] |

subtract from to zero [& record OV] [& record

CR0] |

逻辑、循环和移位指令

PowerPC 提供了一组完整的逻辑操作(指令),还支持对符号的扩展以及对 GPR 中前置零的统计。表 5 列出了 PowerPC 逻辑指令。

表 5. PowerPC 逻辑指令

| 助记符 | 指令名 |

| and[.] | and [& record CR0] |

| andc[.] | and with complement [& record CR0] |

| andi. | and immediate & record CR0 |

| andis. | and immediate shifted & record CR0 |

| eqv[.] | equivalent [& record CR0] |

| nand[.] | not and [& record CR0] |

| nor[.] | not or [& record CR0] |

| or[.] | or [& record CR0] |

| orc[.] | or with complement [& record CR0] |

| oris | or immediate shifted |

| ori | or immediate |

| xor[.] | xor [& record CR0] |

| xoris | xor immediate shifted |

| xori | xor immediate |

| cntlzd[.] | count leading zeros doubleword [& record CR0] |

| cntlzw[.] | count leading zeros word [& record CR0] |

| extsb[.] | extend sign byte [& record CR0] |

| extsh[.] | extend sign halfword [& record CR0] |

| extsw[.] | extend sign word [& record CR0] |

PowerPC 提供了一组健壮而强大的循环和移位操作(指令),如表 6 所列。

表 6. PowerPC 循环和移位指令

| 助记符 | 指令名 |

| rldc[.] | rotate left doubleword then clear [& record CR0] |

| rldcl[.] |

rotate left doubleword then clear left [& record

CR0] |

| rldcr[.] |

rotate left doubleword then clear right [& record

CR0] |

| rldicl[.] |

rotate left doubleword immediate then clear left [&

record CR0] |

| rldicr[.] |

rotate left doubleword immediate then clear right [&

record CR0] |

| rldimi[.] |

rotate left doubleword immediate then mask insert [&

record CR0] |

| rlwimi[.] |

rotate left word immediate then mask insert [&

record CR0] |

| rlwinm[.] |

rotate left word immediate then and with mask [&

record CR0] |

| rlwnm[.] | rotate left word then and with mask [& record CR0] |

| sld[.] | shift left doubleword [& record CR0] |

| slw[.] | shift left word [& record CR0] |

| srad[.] | shift right doubleword [& record CR0] |

| sradi[.] | shift right doubleword immediate [& record CR0] |

| sraw[.] | shift right word [& record CR0] |

| srawi[.] | shift right word immediate [& record CR0] |

| srd[.] | shift right doubleword [& record CR0] |

| srw[.] | shift right word [& record CR0] |

浮点指令

PowerPC 提供了一组健壮的浮点运算、比较和转换操作(指令)。与软件支持一道,PowerPC 浮点运算完全符合 ANSI/IEEE 标准 754-1985 规范。在所有运算和比较操作中都支持单精度和双精度浮点格式。

虽然浮点数以双精度格式存储于 FPR 中,但是,有一组单精度运算指令,可以执行运算操作并将最终结果舍入为单精度,同时检测进行单精度操作时可能会发生的异常(比如指数溢出、下溢和失去精度)。

· 一组 Load Floating-point Single 指令可以访问存储器中的字,并在将其放入目标 FPR 前把单精度值转换为双精度值。

· 一组 Store Floating-point Single 指令可以将源 FPR 中的源操作数在存储到存储器中目标字之前转换为单精度格式。

可以启用或禁用具体种类的浮点异常来支持设陷(trapping) 环境。表 7 列出了基本的和可选的 PowerPC 浮点指令集。

表 7. PowerPC 浮点指令

| 助记符 | 指令名 |

| fmr[.] | FP move [& record CR1] |

| fneg[.] | FP negate [& record CR1] |

| fabs[.] | FP absolute value [& record CR1] |

| fnabs[.] | FP negative absolute value [& record CR1] |

| fadd[s][.] | FP add [single] [& record CR1] |

| fsub[s][.] | FP subtract [single] [& record CR1] |

| fmul[s][.] | FP multiply [single] [& record CR1] |

| fdiv[s][.] | FP divide [single] [& record CR1] |

| fsqrt[s][.] | FP square root [single] [& record CR1] |

| fmadd[s][.] | FP multiply-add [single] [& record CR1] |

| fmsub[s][.] | FP multiply-subtract [single] [& record CR1] |

| fnmadd[s][.] | FP negative multiply-add [single] [& record CR1] |

| fnmsub[s][.] |

FP negative multiply-subtract [single] [& record

CR1] |

| fcmpo | FP compare ordered |

| fcmpu | FP compare unordered |

| fsel[.] | FP select [& record CR1] |

| frsp[.] | FP round to single [& record CR1] |

| fcfid[.] | FP convert from integer doubleword [& record CR1] |

| fctid[z][.] |

FP convert to integer doubleword [& round to zero]

[& record CR1] |

| fctiw[z][.] |

FP convert to integer word [& round to zero] [&

record CR1] |

| fres[.] | FP reciprocal estimate single [& record CR1] |

| frsqrte[.] | FP reciprocal square root estimate [& record CR1] |

FPSCR 处理指令

表 8 列出了基本的 PowerPC FPSCR 处理指令集。

表 8. PowerPC FPSCR 处理指令集

| 助记符 | 指令名 |

| mcrfs | move to CR from FPSCR |

| mffs[.] | move from FPSCR |

| mtfsb0[.] | move to FPSCR bit 0 |

| mtfsb1[.] | move to FPSCR bit 1 |

| mtfsf[.] | move to FPSCR field |

| mtfsfi[.] | move to FPSCR field immediate |

加载和存储指令

所有加载和存储指令的执行都使用 GPR 或者 GPR 和指令中的立即字段作为存储器访问的地址说明符。用指令生成的数据有效地址来更新基址寄存器(也就是 RA)是大部分加载和存储指令的一个可选项。

有用于以下方面的指令:

· 字节、半字、字和双字大小。

· 在 GPR 或 FPR 与存储器之间移动数据。

· 在 GPR 或 FPR 与存储器之间移动数据。

特殊的存储器访问指令包括:

· 多字加载/存储

即

lmw

和

stmw

,可以操作最多 31 个 32 位字。

· 字符串指令

这些指令可以操作最长 128 字节的字符串。

· 内存同步指令

这些用于实现内存同步。CR 的第 2 位(EQ 位) 设置用来记录存储操作的成功完成。内存同步指令包括:

lwarx

/

ldarx

执行加载并设置处理器内部的预留位,编程模型不必明确了解这些行为。如果设置了预留位,相应的存储指令

stwcx.

/

stdcx.

执行条件存储,并清除预留位。

o

lwarx

(加载字并预留变址)

o

ldarx

(加载双字并预留变址)

o

stwcx

(存储字条件变址)

o

stdcx

(存储双字条件变址)

栈

PowerPC 体系结构没有关于本地存储器的栈的概念。体系结构没有定义压入或者弹出指令,也没有定义专门的栈指针寄存器。不过,有一个软件标准可用于 C/C++ 程序,这个标准叫做嵌入式应用程序二进制接口( Embedded Application Binary Interface,EABI),定义了栈寄存器和内存的约定。EABI 将 GPR1 预留为栈指针,GPR3 到 GPR7 用于函数参数传递,GPR3 用于函数返回值。

需要为 C/C++ 提供接口的汇编语言程序必须遵循同样的标准来保持约定。

高速缓存管理指令

PowerPC 体系结构包含了面向应用级高速缓存访问的高速缓存管理指令。高速缓存指令在表 9 中列出。

表 9. 高速缓存管理指令

| 助记符 | 指令名 |

| dcbf | Flush Data Cache Line |

| dcbst | Store Data Cache Line |

| dcbt |

Touch Data Cache Line(for

load) |

| dcbtst |

Touch Data Cache Line(for

store) |

| dcbz | Zero Data Cache Line |

| icbi | Invalidate Instruction Cache Line |

当将高速缓存处理代码移植到不同的 PowerPC 实现时要当心。虽然高速缓存指令可能是跨不同实现而通用的,高速缓存的组织和大小可能会有变化。例如,假定高速缓存大小以对其进行刷新的代码,在用于其他大小的高速缓存时可能需要进行修改。而且,各实现的高速缓存初始化可能不同。有一些实现提供了自动清除高速缓存标签的硬件,而其他实现需要使用软件循环来使高速缓存标签无效。

自修改代码

虽然编写自修改代码不是一个工业标准,但有些情况下是必不可少的。下面的序列介绍了执行代码修改用到的指令:

1. 存储修改的指令。

2. 执行

dcbst

指令,强制包含有修改过的指令的高速缓存行进行存储。

3. 执行

sync

指令,确保

dcbst

完成。

4. 执行

icbi

指令,使将要存放修改后指令的指令高速缓存行无效。

5. 执行

isync

指令,清除所有指令的指令管道,那些指令在高速缓存行被设为无效之前可能早已被取走了。

6. 现在可以运行修改后的指令了。当取这个指令时会发生指令高速缓存失败,结果就会从存储器中取得修改后的指令。

计时器

大部分实现都提供了一个 64 位时基,可以通过两个 32 位寄存器读取,或者通过一个 64 位寄存器读取。各实现的计时器增量不同,SPR 数和访问时基的指令也不同。所以,跨实现移植计时器代码时要当心。另外的计时器可能也不同,但大多数实现都提供了至少一种递减的可编程计时器。

保持代码的兼容性

需要在多个实现上进行编程的 PowerPC 用户通常会问及保持代码兼容性的技巧。下面的建议将有助于尽量减少移植问题:

· 尽可能使用 C 代码。

当今的 C 编译器在很多情况下可以生成与直接手写的汇编代码在性能上相当的代码。作为 Book I 代码,C 代码将保证代码的兼容性。

· 尽可能避免使用处理器相关的汇编指令。

尽量不要在 C 中嵌入处理器相关的汇编指令,因为将更难被发现。分离开那些已知会包含设备相关寄存器或指令的代码。这些通常是启动次序和设备驱动程序,不过也可能包括浮点代码(包括 long long 类型)。保持假定和依赖全部归档。

· 使用处理器版本寄存器(PVR),但只在适当的时候用。

跨差别较小的实现的通用代码还好,PVR 可以用于做出判断。但是,在需要进行较大修改的情况下(例如,PowerPC AS 相对于 Book E MMU 代码),建议使用单独的代码库(code base)。

结束语

PowerPC AS 和 PowerPC 都支持最初的 PowerPC 体系结构中定义的应用级基础设施,同时为具体目标市场提供了最佳的优化。

就其两种操作模式之一而言,PowerPC AS 实质上与最初的 PowerPC 相同,而 PowerPC Book E 在 Book III 级别的定义中,已经走向了不同的方向,为低价格、低功率以及体系结构灵活的嵌入式应用进行了最优化。当然,在 32 位的实现上还不能用双字整数指令,在大部分嵌入式实现中浮点指令也只是通过软件仿真提供支持。

不过,这对应用程序二进制在 PowerPC 体系结构家族树的分支中自由地迁移来说是一个非常有意义的机会。

Powerpc动态

OpenPOWER Summit 2020上,IBM宣布向OpenPOWER社区贡献A2O POWER处理器核心、Open-CE两项关键技术。

继在八月Hot Chips 2020峰会上发布最新IBM POWER10处理器之后,IBM认知系统模拟团队现在又荣幸地推出IBM POWER10功能模拟器。

这一新发布的模拟环境旨在为开发人员提供帮助、方便将现有Linux应用移植到POWER10架构并实现新应用的创建。

8月17日,IBM展示了其下一代的IBM POWER中央处理器(CPU)系列:IBM POWER10。IBM POWER10处理器旨在提供一个平台来满足企业混合云计算的独特需求,采用7纳米工艺,专注于能效和性能的设计。与IBM POWER9处理器相比,预计处理器能效、工作负载能力和容器密度将实现多达三倍的提升。

PowerPC系列产品

海量IBM和NXP PowerPC现货库存

作为IBM和NXP停产(EOL) PowerPC处理器的授权分销商和许可再生产制造商,罗彻斯特电子依然可以持续供应PowerPC产品。PowerPC处理器为32位或64位架构,具有多供应商支持以及广泛的软件和开发工具生态系统。该处理器特别适合各种嵌入式应用的设计,能够广泛应用于通信、网络、医疗、汽车和工业产品。

作为典型的成功复产案例,近期罗彻斯特电子基于IBM裸片复产了50,000颗IBM25PPC750GLECR5H63V,并已成功交付至客户。能够提供满足“63V”版本严格的测试筛选要求的解决方案,并提供可靠性测试, 向客户提供具有长期完整性的产品。罗彻斯特电子已复产该器件,还可实现其它衍生产品的持续生产。

现有PowerPC产品系列包括:

- IBM: 25PPC405xxx、25PPC603xxx、25PPC750xxx

- NXP: MPC5xx, MPC7xx、MPC82xx、MPC83xx、MPC85xx、MCP86xx、MPC87xx、MPC88xx、XPC8260、MPC603

- 罗彻斯特电子复产产品: IBM25PPC750CL、IBM25PPC750CX、IBM25PPC750GX、IBM25PPC750GL、IBM25PPC750FX和IBM25PPC750FL

参考文献链接

https:// mp.weixin.qq.com/s/8tt6 tYlupYFs5AObyD8V6g

https:// mp.weixin.qq.com/s/Pzqo kak-fyLBsFFbE4PgSQ