Verilog以及VHDL所倡导的的代码准则

FPGA/ASIC初学者应该学习Verilog还是VHDL?

-

个人微信公众号: FPGA LAB

-

个人博客首页

-

注:学习交流使用!

Verilog例化方式分为两种,一种是按端口定义时的顺序例化,一种是按端口名来例化。

下面将带来这些内容的叙述以及对比,还有如何处理空置的端口等。

按顺序排列的端口连接是例化的第一种方式,并不推荐,但是必须知道,因为还是有一些代码使用这种例化方式。

如下,如果我设计了一个模块:

module mydesign ( input x, y, z,

output o);

endmodule

那么按端口顺序例化的话,如下所示:

module tb_top;

wire [1:0] a;

wire b, c;

mydesign d0 (a[0], b, a[1], c);

endmodule

还是按上面那个例子,我定了一个模块:

module mydesign ( input x, y, z,

output o);

endmodule

如果按端口名字例化,如下:

module tb_top;

wire [1:0] a;

wire b, c;

mydesign d0(

.x(a[0]),

.y(b),

.z(a[1]),

.o(c)

endmodule

我们推荐使用按名字进行例化的方式,因为这种方式不考虑顺序,不容易出错。

一般自动生成例化模板的软件或插件,也几乎全是生成这种例化模板的。如果生成按顺序例化的模板,那也就注定黄了。

这些都不是重点,重点是下一个话题,我们在做实际项目中也会常常看看有未连接的端口,我们如何认为呢?或者如何处理呢?

未连接到例化模块中的端口按高阻态处理。如下:

还是拿上面设计的模块为例:

module mydesign ( input x, y, z,

output o);

endmodule

我们对这个模块进行例化使用:

module design_top(

input [1:0] a,

output c

mydesign d0 (

.y (a[1]),

.z (a[1]),

.o ());

endmodule

可以看到端口x,就连写都没写,因此,可以认为是一个未连接的悬空端口,是一个高阻态;

端口o,虽然写了,但是也没连接到顶层模块中的任意一个端口上,因此顶层的端口c也是一个高阻态。

下面举一个移位寄存器的例子,看看有些端口未连接,生成的硬件原理图是什么样的。

先从一个触发器看起:

module dff ( input d,

input clk,

input rstn,

output reg q);

always @ (posedge clk) begin

if (!rstn)

q <= 0;

q <= d;

endmodule

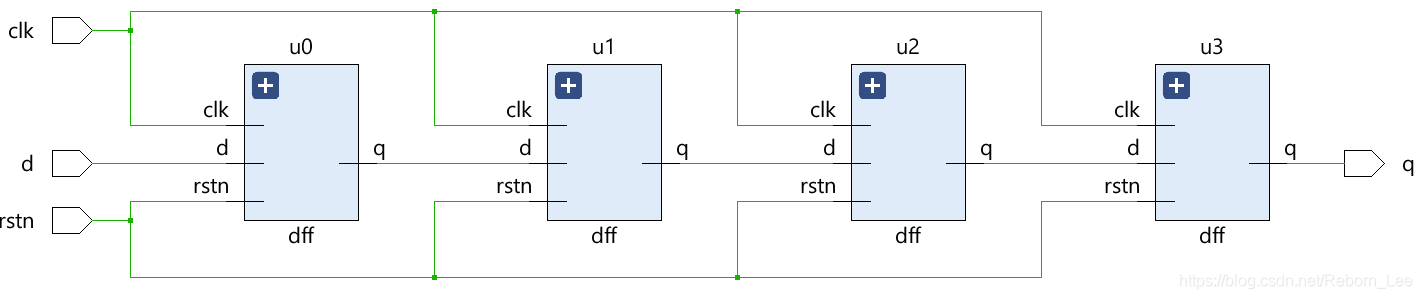

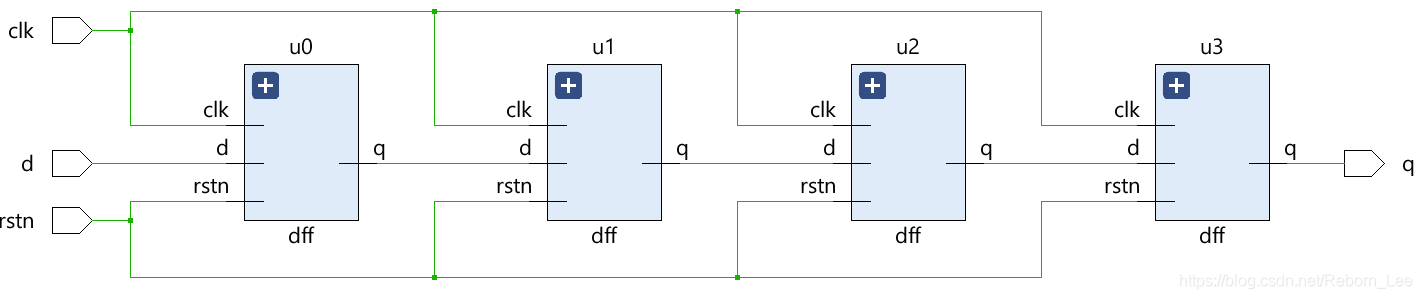

通过例化触发器形成移位寄存器,移位寄存器如果端口都连接了:

module shift_reg ( input d,

input clk,

input rstn,

output q);

wire [2:0] q_net;

dff u0 (.d(d), .clk(clk), .rstn(rstn), .q(q_net[0]));

dff u1 (.d(q_net[0]), .clk(clk), .rstn(rstn), .q(q_net[1]));

dff u2 (.d(q_net[1]), .clk(clk), .rstn(rstn), .q(q_net[2]));

dff u3 (.d(q_net[2]), .clk(clk), .rstn(rstn), .q(q));

endmodule

RTL原理图:

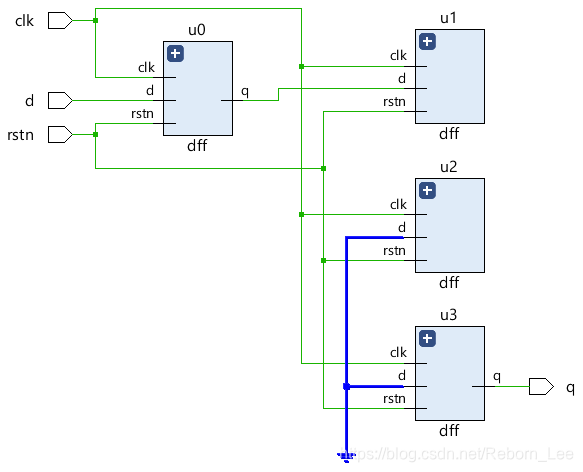

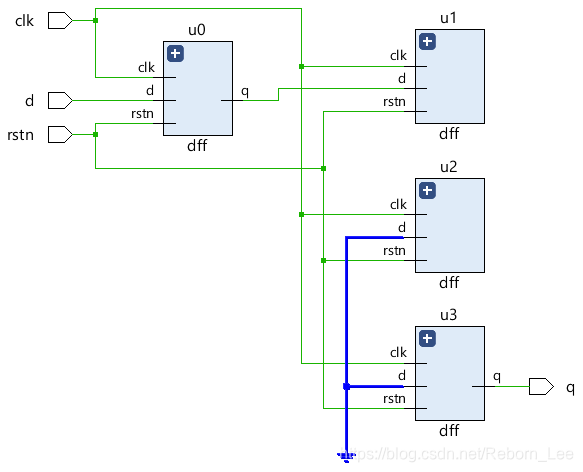

如果有一些端口未连接:

module shift_reg ( input d,

input clk,

input rstn,

output q);

wire [2:0] q_net;

dff u0 (.d(d), .clk(clk), .rstn(rstn), .q(q_net[0]));

dff u1 (.d(q_net[0]), .clk(clk), .rstn(rstn), .q());

dff u2 (.d(q_net[1]), .clk(clk), .rstn(rstn), .q());

dff u3 (.d(q_net[2]), .clk(clk), .rstn(rstn), .q(q));

endmodule

RTL原理图为:

在仿真中,由于端口悬空了,所以,输出也是高阻态z。

所有的端口声明都隐含地声明为wire,因此在这种情况下端口方向就足够了。然而需要存储值的输出端口应该声明为 reg 数据类型,并且可以在程序块中使用,比如 always 和 initial only。

输入或inout类型的端口不能声明为reg,因为它们是由外部连续驱动的,不应该存储值,而是尽快反映外部信号的变化。连接两个不同向量大小的端口是完全合法的,但以向量大小较小的端口为准,而另一个宽度较大的端口的剩余位将被忽略。

所有的端口声明都隐含地声明为wire,因此在这种情况下端口方向就足够了。然而需要存储值的输出端口应该声明为 reg 数据类型,并且可以在程序块中使用,比如 always 和 initial only。输入或inout类型的端口不能声明为reg,因为它们是由外部连续驱动的,不应该存储值,而是尽快反映外部信号的变化。连接两个不同向量大小的端口是完全合法的,但以向量大小较小的端口为准,而另一个宽度较大的端口的剩余位将被忽略。

Verilog例化说明

1.什么是模块例化?为什么要例化?

模块例化可以理解成模块调用。对于一个FPGA工程,通常是由一个顶层模块与多个功能子模块组成,为了实现顶层模块与子模块的连接,需要进行模块间的例化(或说是例化)。在一个FPGA项目工程中,其输入、输出端口命名通常在设计前期就已确定下来,但会存在一些中间变量,一个工程可能会让不同的工程师在不同的时间段内共同完成,不同的人对于这些变量的命名会有所不同,故例化很有必要。

2.实例说明例化方法

实例:静态数码管显示

根据功能将 FPGA 顶层例化了以下两个功

在VHDL设计中,常需要将自己设计的子模块或者实体进行组合,设计复杂的数字电路。在quartus中既可以采用原理图设计方式,对设计实体进行连线,也可以采用VHDL程序实现,采用元器件例化语句。下面以一个利用两个四位加法器设计一个八位加法器的例子,介绍元件例化的方法。

如下是四位加法器的代码,实体输入为四位的a、b两个端口、上一级进位信号cin,输出为四位的运算结果s以及进位信号cout。

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logi

3.5.7 `unconnected_drive和

`nounconnected_drive 18

3.5.8 `celldefine 和 `endcelldefine 18

3.6 值集合 18

3.6.1 整型数 18

3.6.2 实数 19

3.6.3 字符串 20

3.7 数据类型 20

3.7.1 线网类型 20

3.7.2 未说明的线网 23

3.7.3 向量和标量线网 23

3.7.4 寄存器类型 23

3.8 参数 26

第4章 表达式 28

4.1 操作数 28

4.1.1 常数 28

4.1.2 参数 29

4.1.3 线网 29

4.1.4 寄存器 29

4.1.5 位选择 29

4.1.6 部分选择 29

4.1.7 存储器单元 30

4.1.8 函数调用 30

4.2 操作符 30

4.2.1 算术操作符 31

4.2.2 关系操作符 33

4.2.3 相等关系操作符 33

4.2.4 逻辑操作符 34

4.2.5 按位操作符 35

4.2.6 归约操作符 36

4.2.7 移位操作符 36

4.2.8 条件操作符 37

4.2.9 连接和复制操作 37

4.3 表达式种类 38

第5章 门电平模型化 39

5.1 内置基本门 39

5.2 多输入门 39

5.3 多输出门 41

5.4 三态门 41

5.5 上拉、下拉电阻 42

5.6 MOS开关 42

5.7 双向开关 44

5.8 门时延 44

5.9 实例数组 45

5.10 隐式线网 45

5.11 简单示例 46

5.12 2-4解码器举例 46

5.13 主从触发器举例 47

5.14 奇偶电路 47

第6章 用户定义的原语 49

6.1 UDP的定义 49

6.2 组合电路UDP 49

6.3 时序电路UDP 50

6.3.1 初始化状态寄存器 50

6.3.2 电平触发的时序电路UDP 50

6.3.3 边沿触发的时序电路UDP 51

6.3.4 边沿触发和电平触发的混合行为 51

6.4 另一实例 52

6.5 表项汇总 52

第7章 数据流模型化 54

7.1 连续赋值语句 54

7.2 举例 55

7.3 线网说明赋值 55

7.4 时延 55

7.5 线网时延 57

7.6 举例 57

7.6.1 主从触发器 57

7.6.2 数值比较器 58

第8章 行为建模 59

8.1 过程结构 59

8.1.1 initial 语句 59

8.1.2 always语句 61

8.1.3 两类语句在模块中的使用 62

8.2 时序控制 63

8.2.1 时延控制 63

8.2.2 事件控制 64

8.3 语句块 65

8.3.1 顺序语句块 66

8.3.2 并行语句块 67

8.4 过程性赋值 68

8.4.1 语句内部时延 69

8.4.2 阻塞性过程赋值 70

8.4.3 非阻塞性过程赋值 71

8.4.4 连续赋值与过程赋值的比较 72

8.5 if 语句 73

8.6 case语句 74

8.7 循环语句 76

8.7.1 forever 循环语句 76

8.7.2 repeat 循环语句 76

8.7.3 while 循环语句 77

8.7.4 for 循环语句 77

8.8 过程性连续赋值 78

下图显示了一个带有子模块的非常简单的电路 在本练习中,创建模块mod_a的一个实例,然后将模块的三个引脚(in1 in2和out)连接到顶级模块的三个端口(连接a b和out) mod_a模块是为你提供的-你必须实例化它。

在连接模块时,只有模块上的端口是重要的。您不需要知道模块内部的代码。模块mod_a的代码是这样的:

module mod_a ( input in1, input in2...

在使用Verilog进行数字设计或者构建验证平台时,如果连接模块端口的线网或变量的宽度与端口定义的宽度不一致,在进行仿真时将有可能出现逻辑功能与期望不一致的情况,本文将对此类情况进行示例分析。

首先,在IEEE 1364-2001中,模块的端口对于信号的传输类似于连续赋值语句对于信号的传递,因此,对于连续赋值语句的要求也适用于信号通过端口的传递过程(对此可以理解,在具体物理实现后...

花了一个月时间零零碎碎看了下Verilog的语法,终于把Verilog的基本语法学了个大概,可以自己写点小东西了,由于笔者自己都没学完,所以这篇文章肯定不是一篇介绍Verilog语法的方方面面的教程文章(我也没那能耐),而是侧重于写自己学习过程中的一些理念和一些个人认为在学习时必须掌握的一些语法要点。

这里谈一下一些笔者自己学习过程中参考过的资料。首先是《你好FPGA:一本可以听的入门书》这本书,这是一本入门的书,目前笔者自己是看到了第六章,正好把第六章看完。个人感觉这本书讲的是有点浅的,而

3.5.7 `unconnected_drive和

`nounconnected_drive 18

3.5.8 `celldefine 和 `endcelldefine 18

3.6 值集合 18

3.6.1 整型数 18

3.6.2 实数 19

3.6.3 字符串 20

3.7 数据类型 20

3.7.1 线网类型 20

3.7.2 未说明的线网 23

3.7.3 向量和标量线网 23

3.7.4 寄存器类型 23

3.8 参数 26

第4章 表达式 28

4.1 操作数 28

4.1.1 常数 28

4.1.2 参数 29

4.1.3 线网 29

4.1.4 寄存器 29

4.1.5 位选择 29

4.1.6 部分选择 29

4.1.7 存储器单元 30

4.1.8 函数调用 30

4.2 操作符 30

4.2.1 算术操作符 31

4.2.2 关系操作符 33

4.2.3 相等关系操作符 33

4.2.4 逻辑操作符 34

4.2.5 按位操作符 35

4.2.6 归约操作符 36

4.2.7 移位操作符 36

4.2.8 条件操作符 37

4.2.9 连接和复制操作 37

4.3 表达式种类 38

第5章 门电平模型化 39

5.1 内置基本门 39

5.2 多输入门 39

5.3 多输出门 41

5.4 三态门 41

5.5 上拉、下拉电阻 42

5.6 MOS开关 42

5.7 双向开关 44

5.8 门时延 44

5.9 实例数组 45

5.10 隐式线网 45

5.11 简单示例 46

5.12 2-4解码器举例 46

5.13 主从触发器举例 47

5.14 奇偶电路 47

第6章 用户定义的原语 49

6.1 UDP的定义 49

6.2 组合电路UDP 49

6.3 时序电路UDP 50

6.3.1 初始化状态寄存器 50

6.3.2 电平触发的时序电路UDP 50

6.3.3 边沿触发的时序电路UDP 51

6.3.4 边沿触发和电平触发的混合行为 51

6.4 另一实例 52

6.5 表项汇总 52

第7章 数据流模型化 54

7.1 连续赋值语句 54

7.2 举例 55

7.3 线网说明赋值 55

7.4 时延 55

7.5 线网时延 57

7.6 举例 57

7.6.1 主从触发器 57

7.6.2 数值比较器 58

第8章 行为建模 59

8.1 过程结构 59

8.1.1 initial 语句 59

8.1.2 always语句 61

8.1.3 两类语句在模块中的使用 62

8.2 时序控制 63

8.2.1 时延控制 63

8.2.2 事件控制 64

8.3 语句块 65

8.3.1 顺序语句块 66

8.3.2 并行语句块 67

8.4 过程性赋值 68

8.4.1 语句内部时延 69

8.4.2 阻塞性过程赋值 70

8.4.3 非阻塞性过程赋值 71

8.4.4 连续赋值与过程赋值的比较 72

8.5 if 语句 73

8.6 case语句 74

8.7 循环语句 76

8.7.1 forever 循环语句 76

8.7.2 repeat 循环语句 76

8.7.3 while 循环语句 77

8.7.4 for 循环语句 77

8.8 过程性连续赋值 78

8.8.1 赋值—重新赋值 78

8.8.2 force与release 79

8.9 握手协议实例 80

第9章 结构建模 83

9.1 模块 83

9.2 端口 83

9.3 模块实例语句 83

9.3.1 悬空端口 84

9.3.2 不同的端口长度 85

9.3.3 模块参数值 85

9.4 外部端口 87

9.5 举例 89

第10章 其他论题 91

10.1 任务 91

10.1.1 任务定义 91

10.1.2 任务调用 92

10.2 函数 93

10.2.1 函数说明部分 93

10.2.2 函数调用 94

10.3 系统任务和系统函数 95

10.3.1 显示任务 95

10.3.2 文件输入/输出任务 97

10.3.3 时间标度任务 99

10.3.4 模拟控制任务 99

10.3.5 定时校验任务 100

10.3.6 模拟时间函数 101

10.3.7 变换函数 102

10.3.8 概率分布函数 102

10.4 禁止语句 103

10.5 命名事件 104

10.6 结构描述方式和行为描述方式的

混合使用 106

10.7 层次路径名 107

10.8 共享任务和函数 108

10.9 值变转储文件 110

10.9.1 举例 111

10.9.2 VCD文件格式 112

10.10 指定程序块 113

10.11 强度 114

10.11.1 驱动强度 114

10.11.2 电荷强度 115

10.12 竞争状态 116

第11章 验证 118

11.1 编写测试验证程序 118

11.2 波形产生 118

11.2.1 值序列 118

11.2.2 重复模式 119

11.3 测试验证程序实例 123

11.3.1 解码器 123

11.3.2 触发器 124

11.4 从文本文件中读取向量 126

11.5 向文本文件中写入向量 127

11.6 其他实例 128

11.6.1 时钟分频器 128

11.6.2 阶乘设计 130

11.6.3 时序检测器 132

第12章 建模实例 136

12.1 简单元件建模 136

12.2 建模的不同方式 138

12.3 时延建模 139

12.4 条件操作建模 141

12.5 同步时序逻辑建模 142

12.6 通用移位寄存器 145

12.7 状态机建模 145

12.8 交互状态机 147

12.9 Moore有限状态机建模 150

12.10 Mealy型有限状态机建模 151

12.11 简化的21点程序 153

附录 语法参考 157

参考文献 172

3.5.7 `unconnected_drive和

`nounconnected_drive 18

3.5.8 `celldefine 和 `endcelldefine 18

3.6 值集合 18

3.6.1 整型数 18

3.6.2 实数 19

3.6.3 字符串 20

3.7 数据类型 20

3.7.1 线网类型 20

3.7.2 未说明的线网 23

3.7.3 向量和标量线网 23

3.7.4 寄存器类型 23

3.8 参数 26

第4章 表达式 28

4.1 操作数 28

4.1.1 常数 28

4.1.2 参数 29

4.1.3 线网 29

4.1.4 寄存器 29

4.1.5 位选择 29

4.1.6 部分选择 29

4.1.7 存储器单元 30

4.1.8 函数调用 30

4.2 操作符 30

4.2.1 算术操作符 31

4.2.2 关系操作符 33

4.2.3 相等关系操作符 33

4.2.4 逻辑操作符 34

4.2.5 按位操作符 35

4.2.6 归约操作符 36

4.2.7 移位操作符 36

4.2.8 条件操作符 37

4.2.9 连接和复制操作 37

4.3 表达式种类 38

第5章 门电平模型化 39

5.1 内置基本门 39

5.2 多输入门 39

5.3 多输出门 41

5.4 三态门 41

5.5 上拉、下拉电阻 42

5.6 MOS开关 42

5.7 双向开关 44

5.8 门时延 44

5.9 实例数组 45

5.10 隐式线网 45

5.11 简单示例 46

5.12 2-4解码器举例 46

5.13 主从触发器举例 47

5.14 奇偶电路 47

第6章 用户定义的原语 49

6.1 UDP的定义 49

6.2 组合电路UDP 49

6.3 时序电路UDP 50

6.3.1 初始化状态寄存器 50

6.3.2 电平触发的时序电路UDP 50

6.3.3 边沿触发的时序电路UDP 51

6.3.4 边沿触发和电平触发的混合行为 51

6.4 另一实例 52

6.5 表项汇总 52

第7章 数据流模型化 54

7.1 连续赋值语句 54

7.2 举例 55

7.3 线网说明赋值 55

7.4 时延 55

7.5 线网时延 57

7.6 举例 57

7.6.1 主从触发器 57

7.6.2 数值比较器 58

第8章 行为建模 59

8.1 过程结构 59

8.1.1 initial 语句 59

8.1.2 always语句 61

8.1.3 两类语句在模块中的使用 62

8.2 时序控制 63

8.2.1 时延控制 63

8.2.2 事件控制 64

8.3 语句块 65

8.3.1 顺序语句块 66

8.3.2 并行语句块 67

8.4 过程性赋值 68

8.4.1 语句内部时延 69

8.4.2 阻塞性过程赋值 70

8.4.3 非阻塞性过程赋值 71

8.4.4 连续赋值与过程赋值的比较 72

8.5 if 语句 73

8.6 case语句 74

8.7 循环语句 76

8.7.1 forever 循环语句 76

8.7.2 repeat 循环语句 76

8.7.3 while 循环语句 77

8.7.4 for 循环语句 77

8.8 过程性连续赋值 78

8.8.1 赋值—重新赋值 78

8.8.2 force与release 79

8.9 握手协议实例 80

第9章 结构建模 83

9.1 模块 83

9.2 端口 83

9.3 模块实例语句 83

9.3.1 悬空端口 84

9.3.2 不同的端口长度 85

9.3.3 模块参数值 85

9.4 外部端口 87

9.5 举例 89

第10章 其他论题 91

10.1 任务 91

10.1.1 任务定义 91

10.1.2 任务调用 92

10.2 函数 93

10.2.1 函数说明部分 93

10.2.2 函数调用 94

10.3 系统任务和系统函数 95

10.3.1 显示任务 95

10.3.2 文件输入/输出任务 97

10.3.3 时间标度任务 99

10.3.4 模拟控制任务 99

10.3.5 定时校验任务 100

10.3.6 模拟时间函数 101

10.3.7 变换函数 102

10.3.8 概率分布函数 102

10.4 禁止语句 103

10.5 命名事件 104

10.6 结构描述方式和行为描述方式的

混合使用 106

10.7 层次路径名 107

10.8 共享任务和函数 108

10.9 值变转储文件 110

10.9.1 举例 111

10.9.2 VCD文件格式 112

10.10 指定程序块 113

10.11 强度 114

10.11.1 驱动强度 114

10.11.2 电荷强度 115

10.12 竞争状态 116

第11章 验证 118

11.1 编写测试验证程序 118

11.2 波形产生 118

11.2.1 值序列 118

11.2.2 重复模式 119

11.3 测试验证程序实例 123

11.3.1 解码器 123

11.3.2 触发器 124

11.4 从文本文件中读取向量 126

11.5 向文本文件中写入向量 127

11.6 其他实例 128

11.6.1 时钟分频器 128

11.6.2 阶乘设计 130

11.6.3 时序检测器 132

第12章 建模实例 136

12.1 简单元件建模 136

12.2 建模的不同方式 138

12.3 时延建模 139

12.4 条件操作建模 141

12.5 同步时序逻辑建模 142

12.6 通用移位寄存器 145

12.7 状态机建模 145

12.8 交互状态机 147

12.9 Moore有限状态机建模 150

12.10 Mealy型有限状态机建模 151

12.11 简化的21点程序 153

附录 语法参考 157

参考文献 172

3.5.7 `unconnected_drive和

`nounconnected_drive 18

3.5.8 `celldefine 和 `endcelldefine 18

3.6 值集合 18

3.6.1 整型数 18

3.6.2 实数 19

3.6.3 字符串 20

3.7 数据类型 20

3.7.1 线网类型 20

3.7.2 未说明的线网 23

3.7.3 向量和标量线网 23

3.7.4 寄存器类型 23

3.8 参数 26

第4章 表达式 28

4.1 操作数 28

4.1.1 常数 28

4.1.2 参数 29

4.1.3 线网 29

4.1.4 寄存器 29

4.1.5 位选择 29

4.1.6 部分选择 29

4.1.7 存储器单元 30

4.1.8 函数调用 30

4.2 操作符 30

4.2.1 算术操作符 31

4.2.2 关系操作符 33

4.2.3 相等关系操作符 33

4.2.4 逻辑操作符 34

4.2.5 按位操作符 35

4.2.6 归约操作符 36

4.2.7 移位操作符 36

4.2.8 条件操作符 37

4.2.9 连接和复制操作 37

4.3 表达式种类 38

第5章 门电平模型化 39

5.1 内置基本门 39

5.2 多输入门 39

5.3 多输出门 41

5.4 三态门 41

5.5 上拉、下拉电阻 42

5.6 MOS开关 42

5.7 双向开关 44

5.8 门时延 44

5.9 实例数组 45

5.10 隐式线网 45

5.11 简单示例 46

5.12 2-4解码器举例 46

5.13 主从触发器举例 47

5.14 奇偶电路 47

第6章 用户定义的原语 49

6.1 UDP的定义 49

6.2 组合电路UDP 49

6.3 时序电路UDP 50

6.3.1 初始化状态寄存器 50

6.3.2 电平触发的时序电路UDP 50

6.3.3 边沿触发的时序电路UDP 51

6.3.4 边沿触发和电平触发的混合行为 51

6.4 另一实例 52

6.5 表项汇总 52

第7章 数据流模型化 54

7.1 连续赋值语句 54

7.2 举例 55

7.3 线网说明赋值 55

7.4 时延 55

7.5 线网时延 57

7.6 举例 57

7.6.1 主从触发器 57

7.6.2 数值比较器 58

第8章 行为建模 59

8.1 过程结构 59

8.1.1 initial 语句 59

8.1.2 always语句 61

8.1.3 两类语句在模块中的使用 62

8.2 时序控制 63

8.2.1 时延控制 63

8.2.2 事件控制 64

8.3 语句块 65

8.3.1 顺序语句块 66

8.3.2 并行语句块 67

8.4 过程性赋值 68

8.4.1 语句内部时延 69

8.4.2 阻塞性过程赋值 70

8.4.3 非阻塞性过程赋值 71

8.4.4 连续赋值与过程赋值的比较 72

8.5 if 语句 73

8.6 case语句 74

8.7 循环语句 76

8.7.1 forever 循环语句 76

8.7.2 repeat 循环语句 76

8.7.3 while 循环语句 77

8.7.4 for 循环语句 77

8.8 过程性连续赋值 78

8.8.1 赋值—重新赋值 78

8.8.2 force与release 79

8.9 握手协议实例 80

第9章 结构建模 83

9.1 模块 83

9.2 端口 83

9.3 模块实例语句 83

9.3.1 悬空端口 84

9.3.2 不同的端口长度 85

9.3.3 模块参数值 85

9.4 外部端口 87

9.5 举例 89

第10章 其他论题 91

10.1 任务 91

10.1.1 任务定义 91

10.1.2 任务调用 92

10.2 函数 93

10.2.1 函数说明部分 93

10.2.2 函数调用 94

10.3 系统任务和系统函数 95

10.3.1 显示任务 95

10.3.2 文件输入/输出任务 97

10.3.3 时间标度任务 99

10.3.4 模拟控制任务 99

10.3.5 定时校验任务 100

10.3.6 模拟时间函数 101

10.3.7 变换函数 102

10.3.8 概率分布函数 102

10.4 禁止语句 103

10.5 命名事件 104

10.6 结构描述方式和行为描述方式的

混合使用 106

10.7 层次路径名 107

10.8 共享任务和函数 108

10.9 值变转储文件 110

10.9.1 举例 111

10.9.2 VCD文件格式 112

10.10 指定程序块 113

10.11 强度 114

10.11.1 驱动强度 114

10.11.2 电荷强度 115

10.12 竞争状态 116

第11章 验证 118

11.1 编写测试验证程序 118

11.2 波形产生 118

11.2.1 值序列 118

11.2.2 重复模式 119

11.3 测试验证程序实例 123

11.3.1 解码器 123

11.3.2 触发器 124

11.4 从文本文件中读取向量 126

11.5 向文本文件中写入向量 127

11.6 其他实例 128

11.6.1 时钟分频器 128

11.6.2 阶乘设计 130

11.6.3 时序检测器 132

第12章 建模实例 136

12.1 简单元件建模 136

12.2 建模的不同方式 138

12.3 时延建模 139

12.4 条件操作建模 141

12.5 同步时序逻辑建模 142

12.6 通用移位寄存器 145

12.7 状态机建模 145

12.8 交互状态机 147

12.9 Moore有限状态机建模 150

12.10 Mealy型有限状态机建模 151

12.11 简化的21点程序 153

附录 语法参考 157

参考文献 172

例化工具为:auto_inst.exe, 可以把下面链接的附件中的工具小软件auto_inst.exe拷贝到C:\WINDOWS\system32或在环境变量path设置该工具的所在路径。

然后打开dos的命令行界面,cd到需要例化verilog代码的顶层,输入auto_inst -f 需要例化的顶层文件名;

例如auto_inst -f usb20.v

//&port;_begin --------指示生成端口列表

//&instance;("u0", "core\utmi_if.v") -------指示例化模块的例化名及文件相对路径

//&auto;_def -------指示自动生成例化的wire中间变量声明

//®_wire_Begin---------指示自动生成例化wire声明的位置,自动例化生成的wire在//®_wire_Begin 和//®_wire_end之间

//®_wire_end

//&inst;_begin---指示自动例化模块的代码生成的位置,自动生成的例化代码在//&inst;_begin和//&inst;_end 之间

//&inst;_end

每次修改被例化的模块或顶层模块的时候,例化自动生成的代码都不需要做任何修改,工具自动用新的代码替换原来的生成的代码。

3.5.7 `unconnected_drive和

`nounconnected_drive 18

3.5.8 `celldefine 和 `endcelldefine 18

3.6 值集合 18

3.6.1 整型数 18

3.6.2 实数 19

3.6.3 字符串 20

3.7 数据类型 20

3.7.1 线网类型 20

3.7.2 未说明的线网 23

3.7.3 向量和标量线网 23

3.7.4 寄存器类型 23

3.8 参数 26

第4章 表达式 28

4.1 操作数 28

4.1.1 常数 28

4.1.2 参数 29

4.1.3 线网 29

4.1.4 寄存器 29

4.1.5 位选择 29

4.1.6 部分选择 29

4.1.7 存储器单元 30

4.1.8 函数调用 30

4.2 操作符 30

4.2.1 算术操作符 31

4.2.2 关系操作符 33

4.2.3 相等关系操作符 33

4.2.4 逻辑操作符 34

4.2.5 按位操作符 35

4.2.6 归约操作符 36

4.2.7 移位操作符 36

4.2.8 条件操作符 37

4.2.9 连接和复制操作 37

4.3 表达式种类 38

第5章 门电平模型化 39

5.1 内置基本门 39

5.2 多输入门 39

5.3 多输出门 41

5.4 三态门 41

5.5 上拉、下拉电阻 42

5.6 MOS开关 42

5.7 双向开关 44

5.8 门时延 44

5.9 实例数组 45

5.10 隐式线网 45

5.11 简单示例 46

5.12 2-4解码器举例 46

5.13 主从触发器举例 47

5.14 奇偶电路 47

第6章 用户定义的原语 49

6.1 UDP的定义 49

6.2 组合电路UDP 49

6.3 时序电路UDP 50

6.3.1 初始化状态寄存器 50

6.3.2 电平触发的时序电路UDP 50

6.3.3 边沿触发的时序电路UDP 51

6.3.4 边沿触发和电平触发的混合行为 51

6.4 另一实例 52

6.5 表项汇总 52

第7章 数据流模型化 54

7.1 连续赋值语句 54

7.2 举例 55

7.3 线网说明赋值 55

7.4 时延 55

7.5 线网时延 57

7.6 举例 57

7.6.1 主从触发器 57

7.6.2 数值比较器 58

第8章 行为建模 59

8.1 过程结构 59

8.1.1 initial 语句 59

8.1.2 always语句 61

8.1.3 两类语句在模块中的使用 62

8.2 时序控制 63

8.2.1 时延控制 63

8.2.2 事件控制 64

8.3 语句块 65

8.3.1 顺序语句块 66

8.3.2 并行语句块 67

8.4 过程性赋值 68

8.4.1 语句内部时延 69

8.4.2 阻塞性过程赋值 70

8.4.3 非阻塞性过程赋值 71

8.4.4 连续赋值与过程赋值的比较 72

8.5 if 语句 73

8.6 case语句 74

8.7 循环语句 76

8.7.1 forever 循环语句 76

8.7.2 repeat 循环语句 76

8.7.3 while 循环语句 77

8.7.4 for 循环语句 77

8.8 过程性连续赋值 78

8.8.1 赋值—重新赋值 78

8.8.2 force与release 79

8.9 握手协议实例 80

第9章 结构建模 83

9.1 模块 83

9.2 端口 83

9.3 模块实例语句 83

9.3.1 悬空端口 84

9.3.2 不同的端口长度 85

9.3.3 模块参数值 85

9.4 外部端口 87

9.5 举例 89

第10章 其他论题 91

10.1 任务 91

10.1.1 任务定义 91

10.1.2 任务调用 92

10.2 函数 93

10.2.1 函数说明部分 93

10.2.2 函数调用 94

10.3 系统任务和系统函数 95

10.3.1 显示任务 95

10.3.2 文件输入/输出任务 97

10.3.3 时间标度任务 99

10.3.4 模拟控制任务 99

10.3.5 定时校验任务 100

10.3.6 模拟时间函数 101

10.3.7 变换函数 102

10.3.8 概率分布函数 102

10.4 禁止语句 103

10.5 命名事件 104

10.6 结构描述方式和行为描述方式的

混合使用 106

10.7 层次路径名 107

10.8 共享任务和函数 108

10.9 值变转储文件 110

10.9.1 举例 111

10.9.2 VCD文件格式 112

10.10 指定程序块 113

10.11 强度 114

10.11.1 驱动强度 114

10.11.2 电荷强度 115

10.12 竞争状态 116

第11章 验证 118

11.1 编写测试验证程序 118

11.2 波形产生 118

11.2.1 值序列 118

11.2.2 重复模式 119

11.3 测试验证程序实例 123

11.3.1 解码器 123

11.3.2 触发器 124

11.4 从文本文件中读取向量 126

11.5 向文本文件中写入向量 127

11.6 其他实例 128

11.6.1 时钟分频器 128

11.6.2 阶乘设计 130

11.6.3 时序检测器 132

第12章 建模实例 136

12.1 简单元件建模 136

12.2 建模的不同方式 138

12.3 时延建模 139

12.4 条件操作建模 141

12.5 同步时序逻辑建模 142

12.6 通用移位寄存器 145

12.7 状态机建模 145

12.8 交互状态机 147

12.9 Moore有限状态机建模 150

12.10 Mealy型有限状态机建模 151

12.11 简化的21点程序 153

附录 语法参考 157

参考文献 172

端口定义

模块定义以关键字 module 开始,以关键字 endmodule 结束。在module中,对模块的输入和输出进行定义,包括模块名,端口信号,端口声明和可选的参数声明等。

在Verilog中,端口的定义有三种类型, 输入input,输出output和双向端口inout。input、inout 类型不能声明为 reg 数据类型。output 可以声明为 wire 或 reg 数据类型。

具体定义举例如下:

module count(

input i_clk,

input i_r