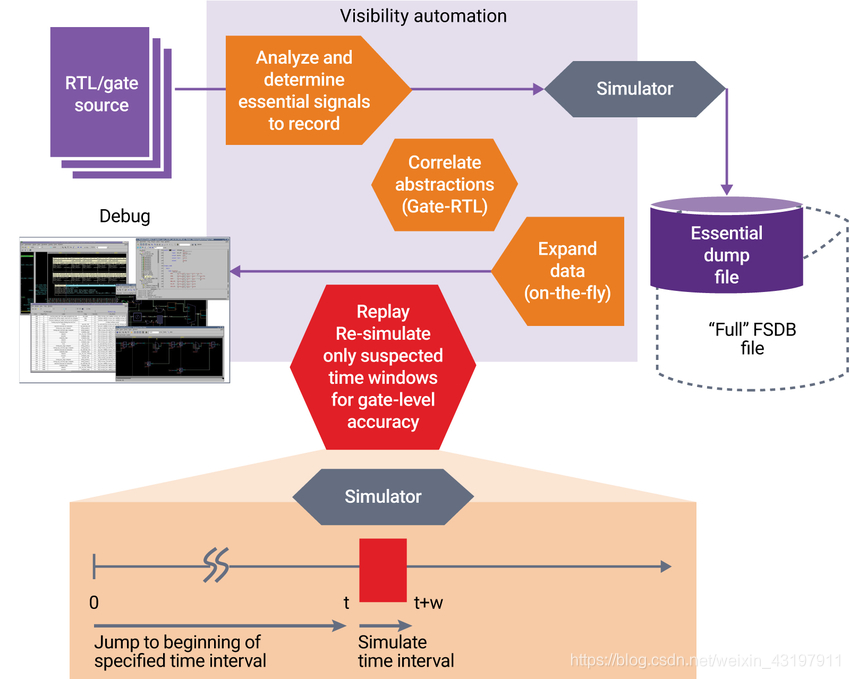

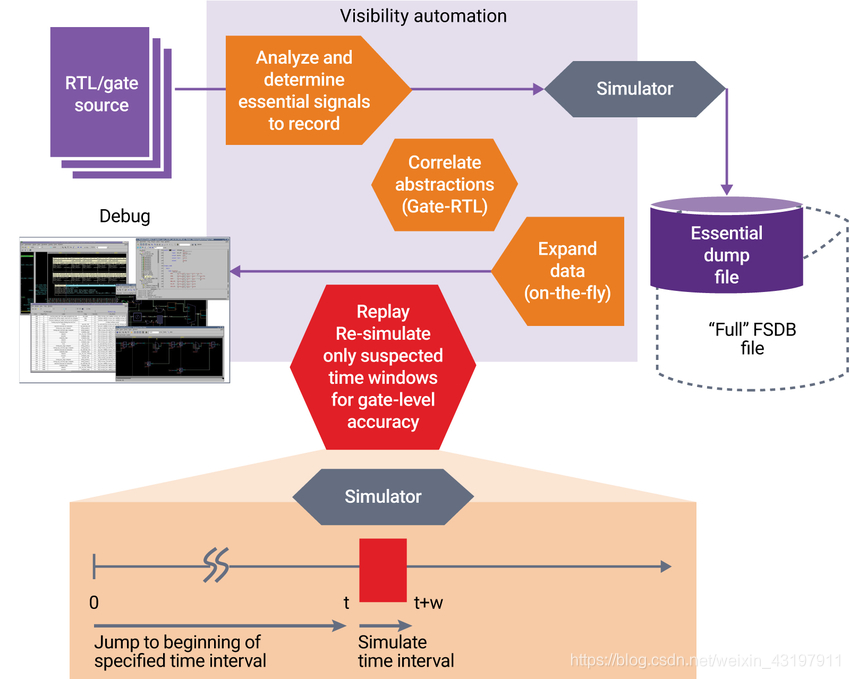

The Siloti™ Visibility Automation System transforms your verification methodology by eliminating the overhead associated with recording data for all the signals in a design. Unique automation technology in the Siloti system provides full visibility of internal signals for complex IC and SoC designs by:

-

Identifying the minimal set of signals that must be recorded

-

Generating “on-demand” the rest of the signal data Correlating

-

gate-level results to the RTL source code

VCS uses VCS compiler scripts to compile the Knowledge Database (KDB) for Verdi. When you specify the -kdb option, VCS creates the Verdi KDB and dumps the design into the libraries specified in the synopsys_sim.setup file.

You can generate the Verdi KDB using the VCS -kdb option either in the VCS two-step flow or three-step flow.

To determine which databases are to be generated, specify one of the following arguments with the -kdb option:

-kdb=only

Generates only the Verdi KDB that is needed for both post-process and interactive simulation debug with Verdi.

In VCS two-step flow, this option does not generate the VCS compile data/executable, and does not disturb the existing VCS compile data/executables.

For example,

% vcs -kdb=only <compile_options> <source files> -lca

In VCS three-step flow, this option dumps the minimum data required at analysis stage, and does not disturb the existing VCS compile data/executables.

% vlogan –kdb=only <vlogan_options> <source files>

The Siloti™ Visibility Automation System transforms your verification methodology by eliminating the overhead associated with recording data for all the signals in a design. Unique automation technolo...

Springsoft,近期宣布旗下关系企业美国Novas公司推出全新精确时序仿真再生技术 ~ Siloti Replay 模块,此功能是属于Siloti信号能见度增强系统Sim VE (Visibility Enhancement) 的附加模块。这项正在申请专利中的新技术可提高芯片仿真过程中所发生时序问题的侦错及修复效率。相较于传统仿真方式,此技术有效提升仿真速度并节省十倍以上的文件存取空间,同时提供芯片侦错过程中,侦错系统所需的精确时序信息。

门级电路(gate level)的时序仿真至今仍是芯片验证流程中普遍使用的方法。Siloti Replay模块大幅降低在时序仿真中对信号转存(s

Verdi用户手册最新版,基于Version U-2023.03, March 2023.Verdi主要用于生成fsdb模型,同VCS使用的vcd文件相比,verdi使用的fsdb相当于vcd文件经过霍夫编码压缩之后的精简版,可用于查看fsdb波形并追踪RTL代码。

虽说verdi、modelsim都是用来调试波形, modelsim与verdi相比,最大的缺点是波形不会全dump,wave窗口拉不全的话需要重新跑,而verdi边运行边查看。具体做法是,在使用tcl指令,在运行仿真时,设置仿真时间,每次run完毕之后,在nWave窗口中file——>自动加载(shift+L快捷键),异常方便!

v

erdi安装目录下会有很多小的工具:

1)波形类型转换类:fsdb2saif,fsdb2vcd,

log2fsdb(只能增加某些周期性信号,从log txt直接产生fsdb波形,适合于

siloti的某些分析)

xml2fsdb

vpd2fsdb,vcd2fsdb;

2)fsdb的波形合并与抽取:fsdbextract,fsdbmerge;

1.3.1 编译型语言和解释型语言

verilog和systemverilog等都是编译型语言,需要使用专门的编译器,针对特定的平台,将源代码一次性的编译成可被该平台硬件执行的机器码,并包装成该平台能识别的可执行程序(simv)的格式。

相对于编译型语言存在的是解释型语言。源代码不是直接翻译成机器语言,而是先翻译成中间代码,再由解释器对中间代码进行解释运行。比如Python/JavaScript / Perl /Shell等都是解释型语言。

解释型语言:程序不需要编译,程序在运行时才翻译成机器语言,每执行一

环境配置

首先搭建好

vcs和V

erdi都能工作的环境,主要有license问题,环境变量的设置。在220实验室的服务器上所有软件的运行环境都是csh。所以,所写的脚本也都是csh的语法。

生成波形文件

Testbench的编写

若想用V

erdi观察波形,需要在仿真时生成fsdb文件,而fsdb在

vcs或者modelsim中的...

一、vcs+verdi常用使用方法

在vcs仿真时调用$dump函数dump出fsdb文件,随后verdi load filelist和fsdb文件来进行debug。

二、debugging with verdi

1、setenv VCS_HOME/VERDI_HOME。

2、vcs编译选项加上-debug_access+all -lca -kdb,-lca表示使用用户限制功能,-kdb是lca下的一个feature,其作用是在vcstwo-step flow

和three-step flow中生成kdb

verdi加载的是Knowledge Database (KDB),这是一个 Elaboration Database elabDB。建议通过 vcs -kdb -lca 生成kdb.elab++,位于simv.daidir目录下。

-lca Limited Customer Availability features are features available with the select functionality. These features will be ready for a gener

报错代码如下:

filelist:11: warning: overriding recipe for target `uvm_dpi.o'

filelist:7: warning: ignoring old recipe for target `uvm_dpi.o'

filelist:13: warning: overriding recipe for target `uvm_dpi.d'

filelist:9

timing check相关的,

+notimingcheck命令,可以用在compile时,也可以用在run time的时候,

都是将检查timing的系统函数,都disable掉了,

加在compile的时候,不会编译到worklib中,速度可快,可以测试gate env;

setuphold,recrem指定的delay sign...