Verilog HDL

详细内容

定义概述

Verilog HDL (Hardware Description Language)是目前应用最广泛的硬件描述语言。它可以用于硬件建模,综合,仿真等。 其最初是于 1983 年由 Gateway Design Automation 公司为其模拟器产品开发的硬件建模语言,1990 年被推向公众领域。 [1]

从语法结构上看,Verilog HDL 语言与 C 语言有许多相似之处,并继承和借鉴了 C 语言的多种操作符和语法结构。它可以用于从算法级、门级到开关级的多种抽象设计层次的数字系统建模。被建模的数字系统对象的复杂性可以介于简单的门和完整的电子数字系统之间。数字系统能够按层次描述,并可在相同描述中显式地进行时序建模。

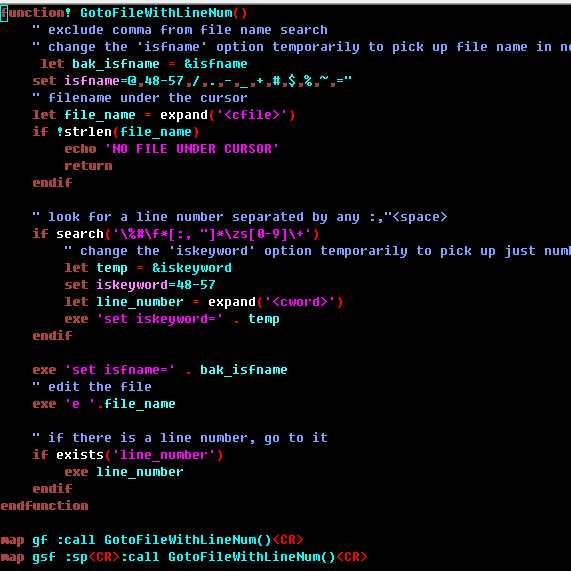

Verilog的发展历程:

硬件描述语言的发展至今已有30多年的历史。

- Verilog HDL语言最初是于1 9 8 3年由Gateway Design Automation 公司为其模拟器产品开发的硬件建模语言。那时它只是一种专用语言。由于他们的模拟、仿真器产品的广泛使用,Verilog HDL 作为一种便于使用且实用的语言逐渐为众多设计者所接受。

- 1989 年,GDA 公司被 Cadence 公司收购,Verilog 语言成为 Cadence 公司的私有财产。

- 1990 年,Cadence 公司成立 OVI(Open Verilog International)组织,公开 Verilog 语言,促进 Verilog 向公众领域发展。

- 1992 年,OVI 决定致力于将 Verilog OVI 标准推广为 IEEE(The Institute of Electrical and Electronics Engineers)标准。

- 1995 年,OVI 的努力获得成功,IEEE 制定了 Verilog HDL 的第一个国际标准,即 IEEE Std 1364-1995,也称之为 Verilog 1.0。

- 2001 年,IEEE 发布 Verilog 第二个标准(Verilog 2.0),即 IEEE Std 1364-2001, 简称为 Verilog-2001 标准。由于 Cadence 在集成电路设计领域的影响力及 Verilog 语言的简洁易用性,Verilog 成为电路设计中最流行的硬件描述语言。 [2]

Verilog HDL的优点

Verilog HDL 语言是一门标准硬件设计语言,采用标准的文本格式,与设计工具和实现工艺无关,从而可以方便地进行移植和重用,它具有多层次的抽象,适合于电子系统设计的所有阶段。由于它容易被机器和人工阅读,因此它支持硬件设计的开发、验证、综合及测试以及硬件设计数据的交流,便于维护、修改和最终硬件电路的获得。Verilog HDL 的特点有以下几点。

(1)简单、直观和高效。

(2)设计可以在多个层次上加以描述,从开关级、门级、寄存器传输级(Register Tansfer Level,RTL)到算法级。

(3)可以用多种不同方式或混合方式对设计建模。

(4)开关级基本结构模型可以使用内置开关级元件进行完整建模。

(5)基本逻辑门可以使用内置门级元件进行完整建模。

(6)提高了逻辑设计的效率,降低设计成本,更重要的是缩短设计周期。

(7)多方位的仿真可以在设计完成之前检测到其错误,减少设计的重复次数,使得第一次投片便能成功实现芯片成为可能。

(8)使检测各种设计方案变得容易和方便,对方案的修改只需要修改 HDL 程序就行了,这比修改原理图要容易得多 。 [3]

由于具有以上这些特点,Verilog HDL 语言已经被绝大多数的 IC 设计者所采用。

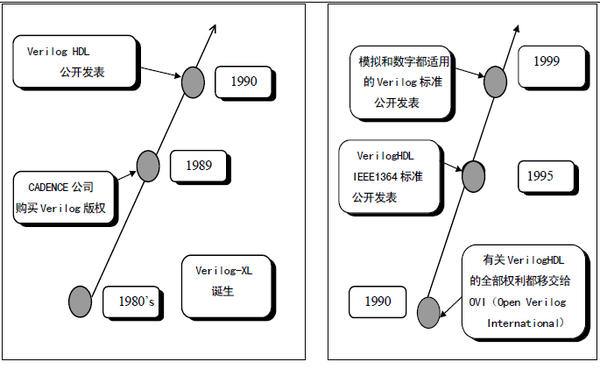

采用硬件描述语言(Verilog HDL)的设计流程简介

自顶向下的设计是从系统级开始 ,把系统划分为若干个基本单元,然后再把每个基本单元划分为下一层次 的基本单元,一直这样做下去 ,直到可以直接用 EDA 元件库中的基本元件来实现为止 。 [4]

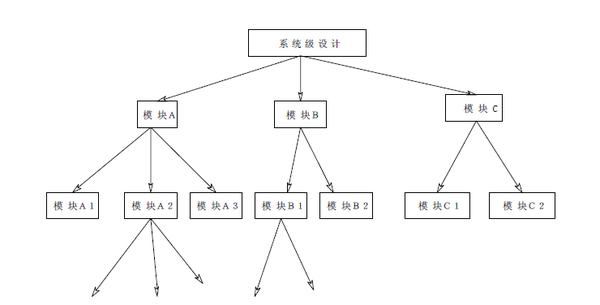

不同抽象级别的Verilog HDL模型

Verilog HDL 是一种用于数字系统设计的语言。用其描述的电路设计就是该电路的 Verilog HDL 模型,也称为模块 。Verilog HDL 既是一种行为描述的语言也是一种结构描述的语言。这就是说 ,无论描述电路功能行为 的模块或描述元器件或较大部件互连 的 模块都可以用 Verilog 语言来建立电路模型。

Verilog 模型可以是实际电路的不同级 别的抽象。这些抽象的级别和它们所对应的模型类 型共有以下5种,现分别给以简述 。

- 系统级( system-level) :用语言提供的高级结构能够实现所设计模块的外部性能的模型。

- 算法级( algorithm level) :用语言提供的高级结构能够实现算法运 行的模型 。

- RTL 级(register transfer level) :描述数据在寄存器之间 的流动和如何处理 、控制这 些数据流动的模型 。

以上三种都属于行为描述 ,只有 RTL 级才与逻辑 电路有明确的对应关系 。

- 门 级( gate-level ) :描述逻辑门以及逻辑门之间连接的模型 。

与逻辑电路有确定的连接关系 ,以上四种数字系统设计工程师必须掌握。

- 开关级( switch-level ):描述器件中三极管和储存节点以及它们之间连接的模型。 [5]

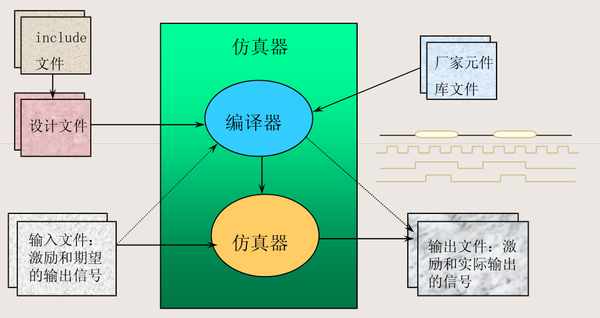

Verilog用于模块的测试

Verilog 还可以用来描述变化的测试信号 。描述测试信号的变化和测试过 程的模块叫做 测试平台(testbench 或 testfixture),它可以对上面介绍的电路模块 (无论是行为的或 结构 的〉进行动态的全面测试 。

一个完整的测试模块应该包含以下几个部分:

- verilog设计文件

- 输入激励信号和输出期望信号

- 编译器和仿真器

- 制造厂家提供的单元库文件

- 输出文件,激励信号的输出对比值

Verilog HDL的基本语法

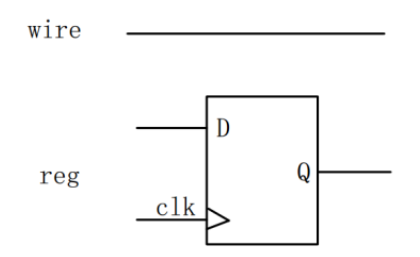

1、变量类型

wire 线型: 用于数据传输,两信号的连接,用assign赋值。

reg 存储器型:

用于寄存器、锁存器、查找表。用always initial赋值。

2、时序电路与组合电路的区别

时序电路:

赋值符号 <= 非阻塞赋值,解释:不受信号延时的影响,输出的结果不受输入信号延时的影响,只根据时钟上升沿或者下降沿变化。

组合电路:

赋值符号 = 阻塞赋值,解释:输出的结果受输入信号延时的影响。

3、时序电路时钟

时序电路,在时钟的上升沿或者下降沿到来时,将触发器D端的数据传输到Q端。

时钟的占空比通常为50%。

4、内部信号上电的默认值定义

例如:reg[7:0] counter = 8'd255;

解释:FPGA一上电,将counter信号赋初始值为8位的十进制数255。只有reg信号且是寄存器才可以赋初始值。wire变量不可以,而且reg组合逻辑也不可以赋初始值。一个信号若不指定位宽,则默认位宽为32位的十进制数。

5、信号位宽的参数化

例如:parameter W = 8;

reg[W-1: 0] counter;

6、赋值语句

用在可综合的:always、assign(功能文件)

用在非可综合的:initial(test bench)

7、组合逻辑与时序逻辑的区别

组合逻辑:不需要时钟,生成组合电路

时序逻辑:有时序节拍,根据时钟延变化,受寄存器节拍控制。

8、运算符

(+、-、*、/、%)加减乘除和取余。

(+、-)可以直接使用

(*、/)调用IP核,%求余数偶尔用一下,这三个符合直接用的话会占用很多的逻辑资源。

!a 等价于 a == 0

reg[1:0] a = 2'b10; 则:&a = a[1] & a[0] = 1 & 0 = 0;

reg[2:0] b = 3'b110; 则:&b = b[2] & b[1] = b[0] = 1 & 1 & 0 = 0;

9、三目运算符(既可用于assign语句,也可用于always语句)

assign a = (b > 6)? 1'b1: 1'b0;

可嵌套:assign a = (b > 6)? 1'b1 : (b < 5)? 1'b1: 1'b0;

10、移位运算符:

>> 右移运算符 每次右移一位,数据高位补0

<< 左移运算符 每次左移一位,数据低位补0

例如:

reg [3:0] a = 4'b0110;

b <= (a >> 1'b1); 则 b 的值为4'b0011;

c <= (a << 1'b1); 则 c 的值为4'b1100;

11、左移位循环可以用以下两种方式实现

(1)用位拼接实现

(2)左移位+判断条件

12、条件判断语句

(1)if...else 最好不大于8级,在模块中顺序执行,上面条件满足则不再执行下面的语句,组合逻辑中最好使用else结束,否则会生成锁存器。

(2)case...endcase 并行执行,最好带有一个default语句,避免有些条件没有列出来。

两个寄存器之间延时较大,容易产生时序违例,时序违例是指:由于延时较大,上一时刻发送的数据,下一时刻采集不到,导致出错。

时序电路不会产生锁存器,组合电路才可能产生锁存器。

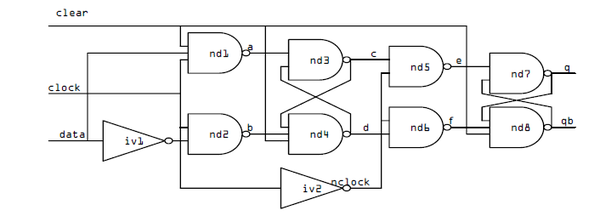

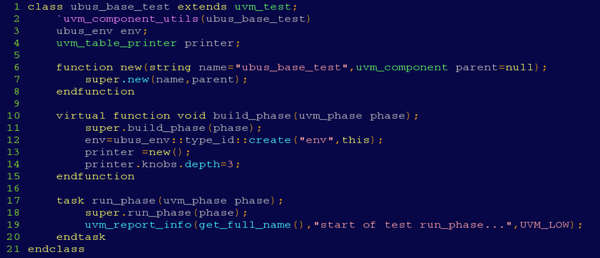

基于以上语法设计一个verilog模块的示意图。

结语

Verilog HDL是目前应用最广泛的硬件描述语言。据有关文献报道,目前在美国使用Verilog HDL进行电路设计的工程师大约有15万人,全美国有200多所大学在教授verilog相关的课程。作为新世纪的大学生和电子工程师,应该掌握Verilog HDL及相关的设计方法,使我国在复杂电路设计系统的竞争中保持竞争力,走在世界前列。