----------------------感谢移知的SV课程------------

在芯片的验证过程中,实施验证通常需要经过以下几个步骤:生成输入激励、捕获输出响应、决定对错、衡量进度、反复迭代。

Verilog模块互联

对Verilog来说,主要通过模块的端口(例化)实现模块之间的互联。例如:

Verilog模块的端提供了一种描述设计中模块之间连接关系的方式, 但不适用与芯片验证,在验证中有很多缺点:

在多个模块中必须重复声明端口

在不同模块中有声明不匹配的风险

设计规范中的一个改动需要修改多个模块

限制了抽象的自顶向下的设计

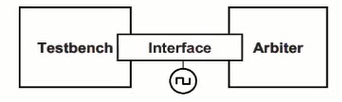

SystemVerilog在Verilog语言基础上扩展了"接口” (interface) 结构,接口给模型提供了一种新的方式,通过使用接口可以简化大型复杂设计的建模和验证。

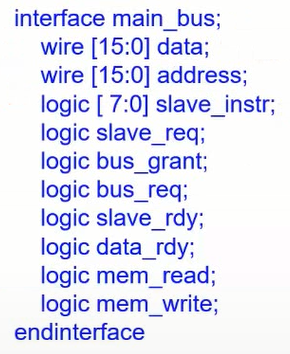

SystemVerilog增加了新的端口类型—接口,接口允许许多信号合成一组由一个端口表示,只需在一个地方对组成接口的信号进行声明,使用这些信号的模块只需一个接口类型的端口。

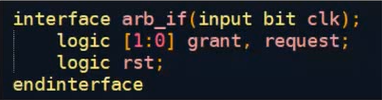

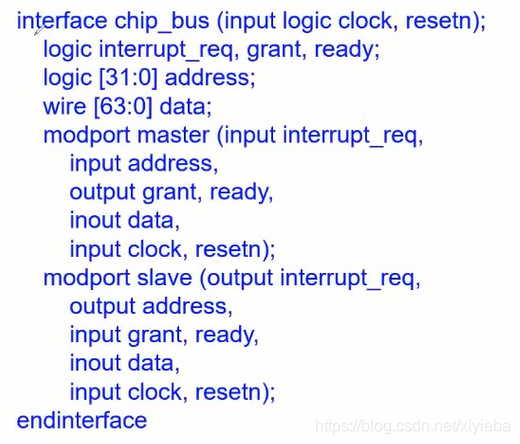

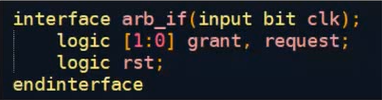

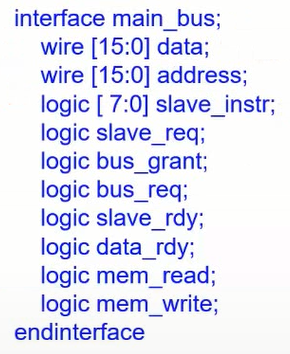

接口使用interface… endinterface声明,将信号包含在其中,封装起来。

接口可以包含类型声明、任务、函数、过程块、程序块和断言。

接口与模块之间有三个不同点: (1) 接口不可以包含设计层次,接口不可以包含模块或原语的实例; (2) 在接口中使用模块则是非法的(3)接口可以包含"modport" ,这使得每个连接到接口上的模块以不同的方式访问接口。

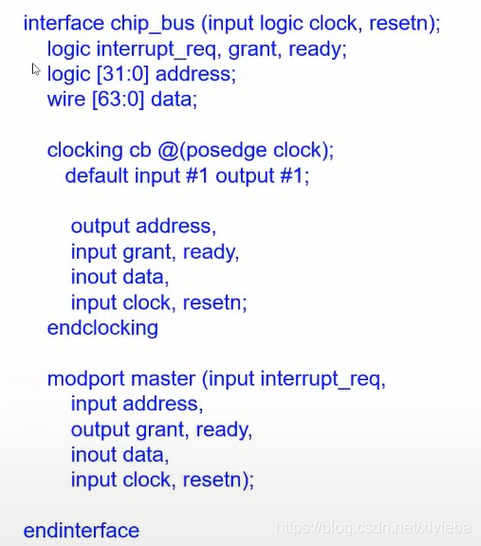

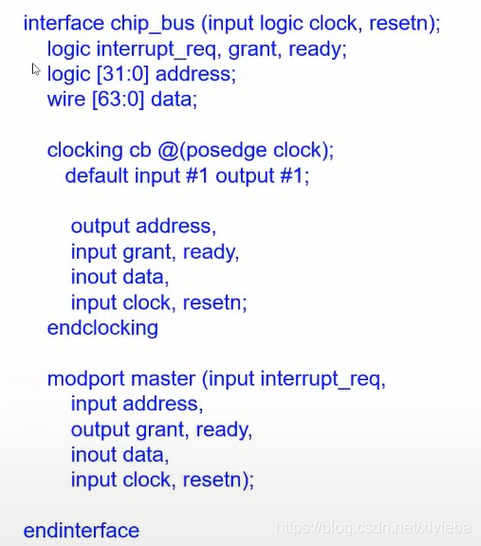

clocking

在interface中,clocking是一个很重要的模块,数字电路很多都是同步的,在clocking中定义时钟触发条件,里面的信号就跟随触发条件同步

其中驱动信号 chip_bus.cp.address <= 32’h8;

引用信号 if(chip_bus.cb.ready)…

重复几个时钟的事件推进repeat(2)@chip.bus.cb;

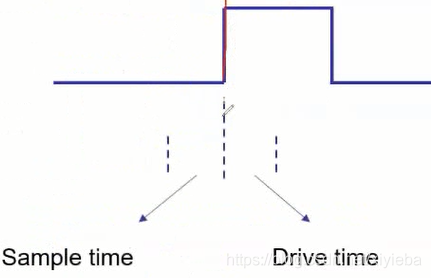

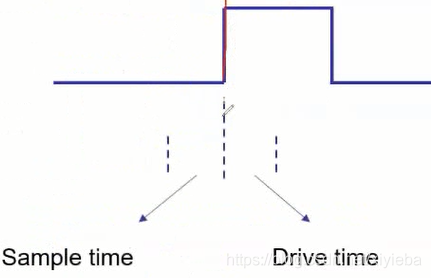

如何理解上面的default input #1 output #1

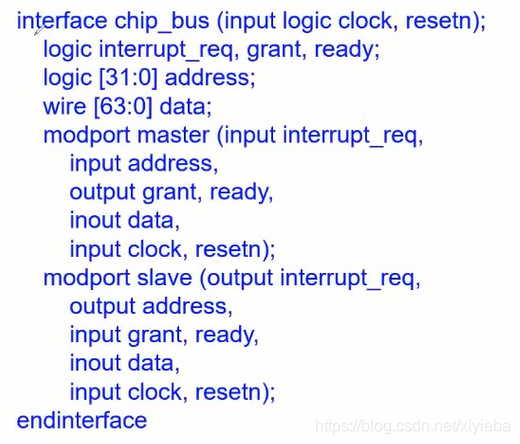

modport

SystemVerilog定义接口时,可以定义接口信号的不同接入方式,以处理不同模块连接到接口端口的方向问题。modport的定义从模块角度描述了接口表示的端口的接入方式,接口中可以有任意数量的modport定义,每个定义描述了各个模块访问接口中的信号。

modport定义中不包含向量位数和类型,这些信息在接口的信号类型声明中定义。事实上modport声明只是使相互连接的模块将信号看成是input、output, inout还是ref。

在复杂设计的接口中,不是每个模块需要访问相同的接口信号,modport为每 个模块创建自己的接口。

通过modport使得模块只可以直接访问在modport定义中列出的信号,达到接口中的某些信号对某些模块隐藏的目的。

接口中可以定义对任何modport都不可见的内部信号,这些信号只能由接口中的协议检查器或其它功能模块使用。

如果连接到接口的模块没有指定modport,模块则可以访问接口中定义的所有信号.

在芯片的验证过程中,实施验证通常需要经过以下几个步骤:生成输入激励、捕获输出响应、决定对错、衡量进度、反复迭代。Verilog模块互联对Verilog来说,主要通过模块的端口(例化)实现模块之间的互联。例如:Verilog模块的端提供了一种描述设计中模块之间连接关系的方式, 但不适用与芯片验证,在验证中有很多缺点:在多个模块中必须重复声明端口在不同模块中有声明不匹配的风险设计规范中的一个改动需要修改多个模块限制了抽象的自顶向下的设计SystemVerilog在Verilog语言基础上扩展

在verilog中每当遇到复杂的模块时,我们都不得不书写一长串端口声明,稍有不慎就会写错,并且难以检查。但在systemverilog中,接口interface则是避免了这个问题。下面的代码是对一个一位加法器的验证,使用了接口。`timescale1ns/1ps

interfaceif_port(inputbitclk);//声明接口

lo...

文章目录概念一、特点二、modport三、clocking时钟块四、参数传递五、SVA断言和断言覆盖率六、产生时钟和复位信号

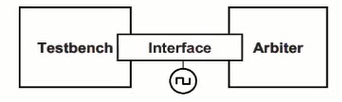

随着设计的日益复杂,设计中的不同功能的设计会被切割成不同的模块,模块与模块之间通信端口随着设计的复杂程度增加而变得很多,测试平台与不同模块和子模块DUT之间的端口连接也就变得更加复杂。这时,如果我们仍然采用对每个端口一一连接的方式,显然是有很承重的负担,日后代码的维护工作也变得很困难。接口就起到一根很粗电缆线的作用,连接着设计与验证环境。

如下,当两个模块module之间不采用

2.6.2 本节引言

给FPGA一个支点,它可以撬动整个数字逻辑。““给我一根杠杆我就能撬动地球”是古希腊数学家、物理学家阿基米德说的,这句话是阿基米德的经典语录,这句话还被翻译为“给我一个支点,我就能撬起整个地球”,用了夸张的方式来说明杠杆原理。”

2.6.3

1. Interface概念

System Verilog中引入了接口定义,接口与module 等价的定义,是要在其他的接口、module中直接定义,不能写在块语句中,跟class是不同的。

接口是将一组线捆绑起来,可以将接口传递给module。

2. 接口的优点

一)通过接口在module之间或内部进行信号,模块的输入列表就是一个接口,这样简单,避免手动连线的错误..

SystemVerilog for Verification teaches the reader how to use the power of the new SystemVerilog testbench constructs plus methodology without requiring in-depth knowledge of Object Oriented Programming or Constrained Random Testing. The book covers the SystemVerilog verification constructs such as classes, program blocks, C interface, randomization, and functional coverage. SystemVerilog for Verification also reviews some design topics such as interfaces and array types. There are extensive code examples and detailed explanations. The book will be based on Synopsys courses, seminars, and tutorials that the author developed for SystemVerilog, Vera, RVM, and OOP. Concepts will be built up chapter-by-chapter, and detailed testbench using these topics will be presented in the final chapter. SystemVerilog for Verification concentrates on the best practices for verifying your design using the power of the language.