数字IC后端实现面试精选300问(后端面试系列连载)

今天小编将继续分享数字IC后端实现面试精选专题,希望对大家有所帮助。整个连载系列300问会持续更新,力争在校招开始前更新完毕。完整的300问分享最后会整理到小编的知识星球上(公众号不会全部放出)。只要认真看小编公众号和知识星球内容的朋友,找份好工作真的非常简单。

小编知识星球属于付费社群,目前已经拥有 530位 铁杆粉丝。本着志愿加入的原则,每年208元,相当于 0.57元/天 。每天少吃半个鸡蛋,这点钱就出来了。

一个人可以走的很快,但一群人可以走的很远。这就是抱团学习的效果。 一个人能走的有多远,关键看他与谁同行。

知识星球用户已经到期,需要续费的朋友,可以直接扫描或长按识别即可( 七折续费 )。

本知识星球运营已有两年多,积累了大量的问答和资料(问答已经高达 近17K )。为方便各位星友快速搜索相关资料和解决相关疑问,目前正在对知识星球上的问答和主题进行标签整理工作。各位星友可以按照以下指引,搜索对应 标签 进行精确搜索,搜索不区分大小写。

1. 与 流程相关 的问题可以搜索 #DC# #DFT# #Floorplan# #Powerplan# #placement# #CTS# #Route# #DFM# #PT# #DRC# #lvs# #功耗分析# #形式验证# #hierarchy flow# #后仿# #PV#

2. 与 后端学习、面试以及职业生涯规划相关 的问题可以搜索 #学习资料# #建议&职业规划# #专利# #培训# #后端面试# #模拟# #服务器# #DDR#

3. 与 时序概念相关 的问题可以搜索 #Timing# #setup# #hold# #transtion# #fanout# #OCV# #time budget# #multicycle path# #clock uncertain# #latch up# #slew# #noise# #drv# #correlation# #io latency# #Crosstalk# #SDC# #复位# #net delay# #PVT# #signoff#

4. 与 电源网格和功耗概念相关 的问题可以搜索 #SSO# #IR drop# #VCD# #apl# #low power# #upf# #power domain# #power budget# #level shifter# #power switch# #ESD# #secondary power#

5. 与 时钟树概念相关 的问题可以搜索 #CTS# #clock mesh# #icg# #OCC电路结构# #cts constraint# #data balance# #clock latency# #分段长tree# #physically_excl##clock skew# #tiehi&tielow#

6. 与 EDA工具相关 的问题可以搜索 #PT# #tempus# #Redhawk# #Milkyway##Virtuoso# #DMSA# #ptpx# #PBA# #voltus# #DC# #ICC2# #innovus#

7. 与 工艺库设置相关 的部分问题可以搜索 #site# #单位设置# #ecsm# #library设置# #工艺# #spare cell # #Trace net# #RDL# #NDM# #tluplus# #SMIC# #MMMC# #ETM# #track#

8. 与 floorplan分析相关 的问题可以搜索 #数据流# #利用率# #congestion# #blockage# #IO# #density# #bounds#

9. 与 ECO相关 的问题可以搜索 #ECO# #guide buffer# #spare cell# #short# #insert spare ce# #copy net# #diff net space#

10. 与 DFM相关 的问题可以搜索 #filler# #redundant via# #antenna# #dummy# #decap cell# #EM#

11. 与 命令和脚本相关 的问题可以搜索 #脚本#

12. 其他概念可以搜索 #seal ring# #mvrc# #magnet placemen# #dbget# #terminal# #floating port# #指针# #v2lvs# #placement block# #stream out# #自动摆放port# #flip chip# #merge# #delay line结构#

好了,下面进入今天的主题分享。

21. CTS后需要分析setup和hold吗?CTS后如何分析时钟树是否合理?

一般情况CTS仅仅是build clock tree,并不做timing optimization。不论是S家还是C家都一样。S的post-cts timing optimization可以通过psynopt或clock_opt来实现。C的post-cts timing optimization可以通过optDesign -postCTS来实现。

Clock Tree的合理性主要通过以下几点来衡量:

- Clock tree latency

- Clock skew

- clock timing drc

- clock tree leakage

想成为数字IC时钟树综合(clock tree synthesis)专家,建议好好看看这个!

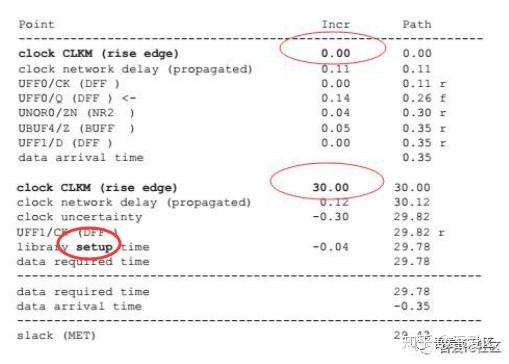

22. 给定一个timing report,要求判断这条path是setup还是hold的timing report? 要求判断当前的report是什么阶段的report?分析该条path是否有异常(比如某个delay值比较大等等)?

下图为一个setup的report,而且是长好tree的report。

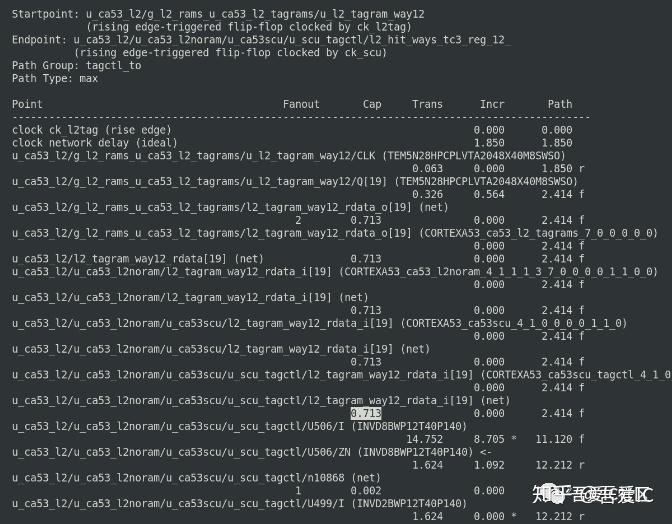

下面这条path为小编知识星球上一个星友提问的问题。请问这条path的timing report正常吗?如果有问题,大家猜猜是什么问题?

23. 阐述下clock inter-balance是干什么用的?分析其存在的合理性。

如果时钟是同源的,那么工具默认会做同步。但是有些时钟不是同源的,cts constraint中是通过create_clock来定义的两个时钟A和B。这两个clock domain又需要交互,那么这时候就可以通过做clock的inter-balance来实现设计需求。

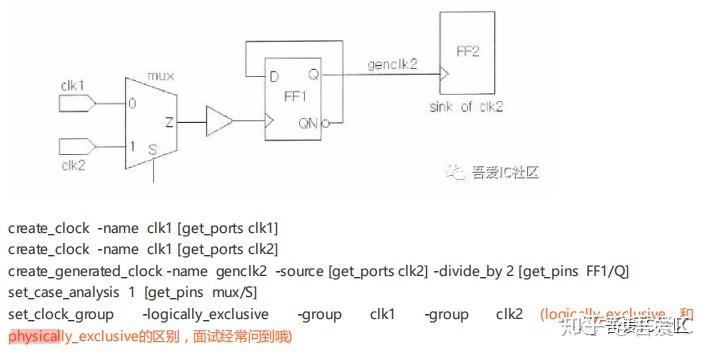

24. 阐述下logic exclusive和physical exclusive的区别。

简单总结:logic exclusive是逻辑上互斥,physical exclusive是物理位置互斥。比如之前分享的这个案例,clk1和clk2设置clock group时就应该设置logic exclusive。

25. 如何实现某几路data path上的delay值接近?

可以把data当做clock tree来做,然后通过clock的inter-balance来实现。

26. 阐述Create_clock和create_generated_clock的区别和联系?在cts阶段,这两种constraint下,工具的行为有何不同?

一句话概括。Create_clock出来的时钟是独立的,是自己长自己的tree,而create_generated_clock定义的时钟是需要同master clock做同步的。

27. 如何计算电路最高工作频率(需要特别注意时钟占空比不是1:1的情况)?

2019年数字IC后端校招笔试题目(附数字后端培训视频教程)

28. 如果从下面的两个芯片中选一个给你做数字后端设计实现,你要选哪个?请说明理由?

(1) 宽 = 3倍的长(2) 长 = 3倍的宽

根据设计所采用的metal stack以及powerplan设计(哪些层是用来专门画power的),估算出H和V的routing resource,如果H的多,就选宽的,反之,就选高的。

当然实际项目中受芯片尺寸等因素影响,很多时候block的形状并不能完全按照这个标准来做。但是大部分模块的绕线并不都是都比较难绕线,而且也不会真正做到绕线的极限。所以实际项目中往往仅仅是高频模块,绕线困难的模块才要尽量遵守这样的规则。

29. 阐述何为Core limitted,何为IO Limitted?针对Core limitted的design,应该从哪些方面着手减少芯片面积?针对IO Limitted的design,应该如何减少面积?

对于一个IO/PAD Limitted的芯片,它的面积受限于IO/PAD的数量。因为芯片中IO的数量太多,导致芯片的长宽拉的比较大。对于这种情况,可以考虑对 IO进行精简 ,比如去掉一些不太重要的IO或对IO进行 复用 等。

对于一个CORE Limitted的芯片,它的面积受限于芯片中各个子模块的面积大小。对于这种情况,各个子模块的数字后端实现就必须加大火力进行抠面积,将利用率最到最高,从而将芯片做小。

30.如果一颗芯片中有很多的IO Domain,需要注意哪些问题?阐述下每个IO Domain中应该包括哪些cell?

- 各个IO Domain内的IO顺序

- 各IO Domain的SSO计算

- 各个IO Domain之间的cut cell

- 整芯片的IO Bus检查

各个IO Domain主要包括给core供电的vdd/vss,给IO供电的VDD/VSS以及一些physical cell。更多详细信息可以查阅之前分享的这篇文章。

IO Ring的设计等详细教程可以移步小编知识星球,有一份非常详细的技术文档。

好了,今天的内容分享就到这里。如果小编的分享对你有所帮助,帮忙点击 “在看” 并转发给你的朋友,算是对小编的一点帮助。

小编知识星球简介(如果你渴望进步,期望高薪,喜欢交流,欢迎加入):

在这里,目前已经规划并正着手做的事情:

- ICC/ICC2 lab的编写

- 基于ARM CPU的后端实现流程

- 利用ICC中CCD(Concurrent Clock Data)实现高性能模块的设计实现

- 基于ARM 四核CPU 数字后端Hierarchical Flow 实现教程

- 时钟树结构分析

-

低功耗设计实现

定期将项目中碰到的问题以案例的形式做技术分享

吾爱IC社区 知识星球星主为公众号”吾爱IC社区”号主,从事数字ic后端设计实现工作近八年,拥有 55nm,40nm,28nm,22nm,14nm 等先进工艺节点成功流片经验,成功 tapeout过三十多颗芯片 。

这里是一个数字IC设计实现高度垂直细分领域的知识社群,是数字IC设计实现领域中最大,最高端的知识交流和分享的社区,这里聚集了无数数字ic前端设计,后端实现,模拟layout工程师们。

在这里大家可以多建立连接,多交流,多拓展人脉圈,甚至可以组织线下活动。在这里你可以就数字ic后端设计实现领域的相关问题进行提问,也可以就职业发展规划问题进行咨询,也可以把困扰你的问题拿出来一起讨论交流。对于提问的问题尽量做到有问必答,如遇到不懂的,也会通过查阅资料或者请教专家来解答问题。在这里鼓励大家积极发表主题,提问,从而促进整个知识社群的良性循环。每个月小编会针对活跃用户进行打赏。

最重要的是在这里,能够借助这个知识社群,短期内实现年薪百万的梦想!不管你信不信,反正已经进来的朋友肯定是相信的!相遇是一种缘分,相识更是一种难能可贵的情分!如若有缘你我一定会相遇相识!知识星球二维码如下,可以扫描或者长按识别二维码进入。目前已经有530 位 星球成员,感谢这 530 童鞋的支持!欢迎各位渴望进步,期望高薪的铁杆粉丝加入! 终极目标 是打造实现本知识星球 全员年薪百万的宏伟目标 。