task automatic test_flag ;

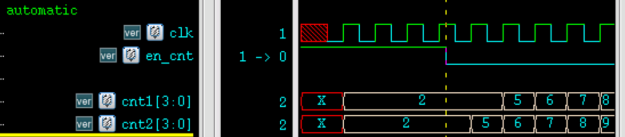

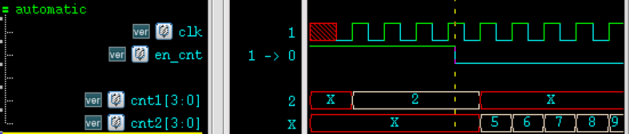

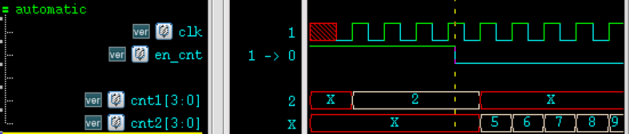

此时仿真结果如下:

en_cnt 为高时,任务 (1) 中信号 cnt1 能输出正确的逻辑值,任务 (2) 中信号 cnt2 的值为 X;

en_cnt 为低时,任务 (2) 中信号 cnt2 能输出正确的逻辑值,任务 (1) 中信号 cnt1 的值为 X;

可见,任务在两次并发调用中,因为存储空间相互独立,信号间并没有产生影响。

结构建模方式有 3 类描述语句: Gate(门级)例化语句,UDP (用户定义原语)例化语句和 module (模块) 例化语句。本次主要讲述使用最多的模块级例化语句。文章目录5.1 Verilog 模块与端口模块端口inout 端口仿真5.2 Verilog 模块例化命名端口连接顺序端口连接端口连接规则5.1 Verilog 模块与端口模块模块是 Verilog 中基本单元的定义形式,是与外界交互的接口。模块格式定义如下:module module_name #(parameter_l

所有的端口声明都隐含地声明为wire,因此在这种情况下端口方向就足够了。然而需要存储值的输出端口应该声明为 reg 数据类型,并且可以在程序块中使用,比如 always 和 initial only。

输入或inout类型的端口不能声明为reg,因为它们是由外部连续驱动的,不应该存储值,而是尽快反映外部信号的变化。连接两个不同向量大小的端口是完全合法的,但以向量大小较小的端口为准,而另一个宽度较大的端口的剩余位将被忽略。

Verilog module 模块例化与简单层次电路设计

在上节课中我们介绍了在Verilog 中,逻辑电路的入口及行为描述。语法规则非常简单,说穿了就是数字电路的文字描述。也就在数字电路中的单一电路都可以用这种方法进行描述。但是在数字电路设计中,复杂电路往往是由多个子电路或器件实现的,在Verilog中是如何对应的呢?

在Verilog 结构中可以通过例化的方式实现设计的层次结构。本节课程中我们将以1位全加器的设计,例化(instance), 然后在4位全加器中引用为例介绍如何通过这种方式,实现层次电

一个模块能够在另外一个模块中被引用, 这样就建立了描述的层次。模块实例化语句形式如下:

module_name instance_name(port_associations) ;

连接信号到模块端口

有两种常用的方法将信号连接到端口上:位置和名称。

通过位置将信号连到端口上的语法应该比较熟悉,因为这是类c语言的语法。当实例化一个模块时,根据这个模块声明时的端口顺序从...

最近在做nandflash的擦写,要用VHDL编写激励文件做仿真,之前一直用的Verilog,现在总结如何用VHDL语言编写testbench。

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

entity (测试平台名)is

end...